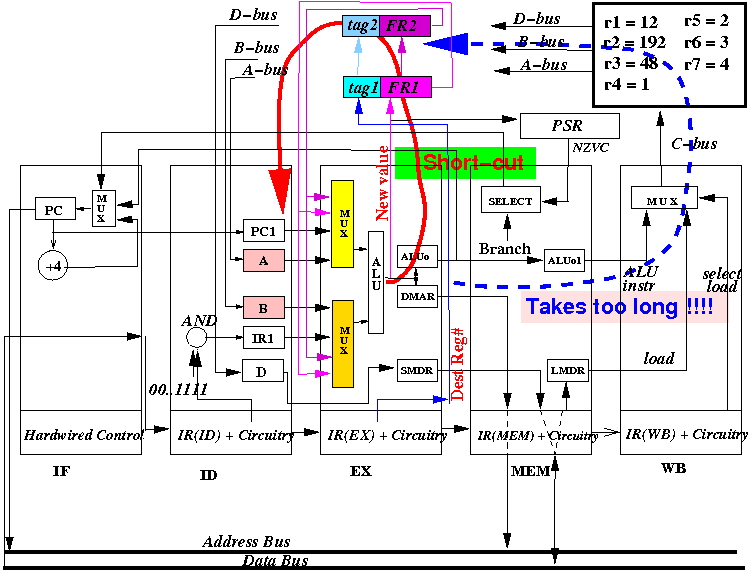

Solution: we add a short-cut to allow the ID stage to fetch the new value(s) ASAP

I will now illustrate the solution using an example

Example program with (multiple) read-after-write data hazard:

I will show you how data forwarding circuitry operates using these instructions

Cycle 1: instruction add r1,r2,r3 fetched into IR(ID):

The ID stage will fetch the operands while the IF stage will fetch the next instruction

Start 2: ID stage fetches operands R2,R3, IF stage fetch add r4,r1,r4

End 2: Operands R2,R3 fetched, add r4,r1,r4 fetch

Notice I have shown the instruction codes (with source and destination reg #'s)

Start 3: EX stage adds R2+R3, ID stage fetches operands R4,R1, IF stage fetch add r5,r1,r5

Notice the ID stage fetches an old value from R1 - new R1 value is being computed in EX stage

End 3: R2+R3 stored in ALUo and FW1 !!

Notice the new R1 value in FR1 is available as operand through the MUX !!!

Start 4: MEM: No op , EX: adds R4+R1, ID stage fetch R5,R1, IF stage fetch add r6,..

Notice: MUX detects that srg reg #1 == tag1 and selects FR1 as operand #1 !!!

End 4: EX: computes 240+1, new R1 stored in FW2 and can be used by next instruction !!

Notice the new R1 value in FR2 is available as operand for one more instruction !!!

Start 5: MEM: No op , EX: adds R5+R1, ID stage fetch R6,R1, IF stage fetch add r7,..

Notice: MUX detects that srg reg #1 == tag2 and selects FR2 as operand #1 !!!

End 5: EX: computes 240+2 --- the new R1 is no longer needed (removed from FW regs) !!

Notice the new R1 value no longer in the forwarding registers (because the ID stage can get the new value from the register R1 from now on !!!)

|