What have we learned so far:

|

In the remainder of the course, we will study techniques to execute multiple instructions:

|

The CPU that we have studied operates as follows:

|

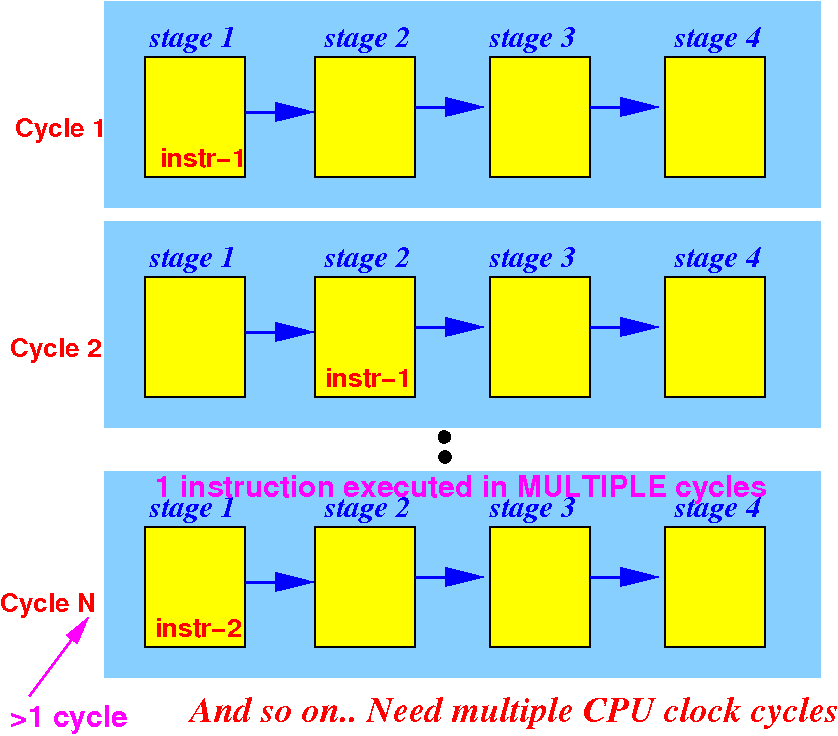

All these steps (= stages of processing) are performed completely for one instruction before the next instruction is fetched from memory...

The "normal" CPU processes program instructions as follows

Initial state:

The stages represents the various steps of the instruction execution cycle

The "normal" CPU processes program instructions as follows

(1) Fetch the Instruction-1 from memory:

The diagram depicts that instruction-1 has now completed its stage 1 of processing

The "normal" CPU processes program instructions as follows

(2) Fetch the operands for Instruction-1 from the registers:

The diagram depicts that instruction-1 has now completed its stage 2 of processing

The "normal" CPU processes program instructions as follows

(3) Perform the computation on the operands of Instruction-1:

The diagram depicts that instruction-1 has now completed its stage 3 of processing

The "normal" CPU processes program instructions as follows

(4) Write (= store) the result of Instruction-1 back into a register:

The diagram depicts that instruction-1 has now completed its stage 4 of processing

Now the execution of instruction-1 is completed and instruction-2 is then fetched and processed !

The "normal" CPU processes program instructions as follows

(5) Fetch the Instruction-2 from memory:

The diagram depicts that instruction-2 has now completed its stage 1 of processing

And so on...

|

The pipelined CPU processes program instructions as follows

Initial state:

The stages represents the various steps of the instruction execution cycle

The pipelined CPU processes program instructions as follows

(1) Fetch the Instruction-1 from memory:

The diagram depicts that instruction-1 has now completed its stage 1 of processing

The pipelined CPU processes program instructions as follows

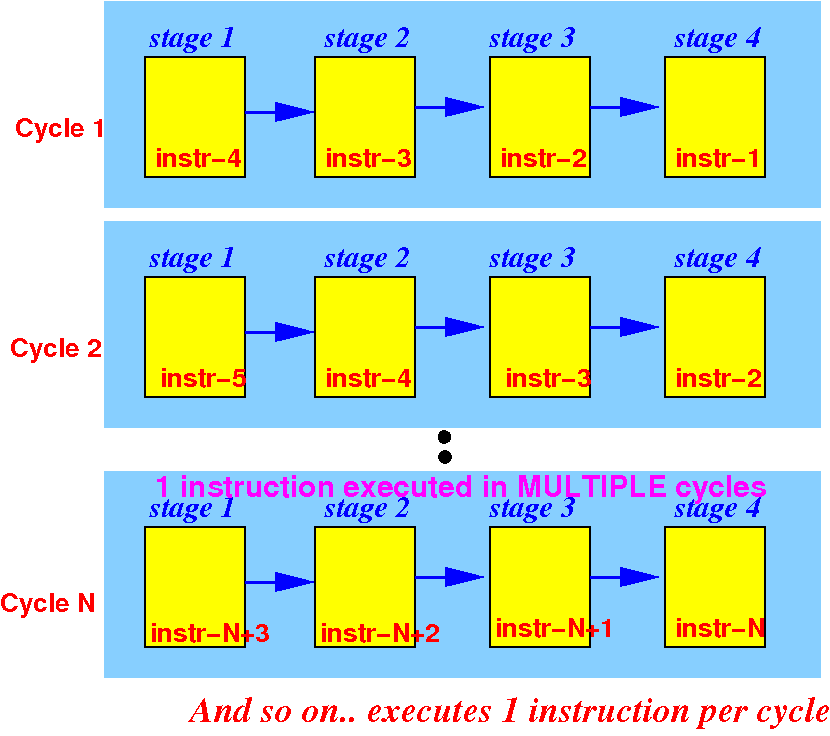

(2) (A) Fetch the operands for Instruction-1 (2) and fetch instruction-2 from memory:

Instruction-1 completed its stage 2 of processing and instruction-2 completed its stage 1

The pipelined CPU processes program instructions as follows

(3) (A) Perform the computation on the operands of Instruction-1, (B) Fetch operands for Instruction-2 and (C) fetch Instruction-3 from memory:

Instruction-1 completed its stage 3 of processing, Instruction-2 completed its stage 2 and Instruction-3 completed its stage 1

A non-pipelined CPU executes 1 instruction in N (> 1) CPU clock cycles:

A pipelined CPU executes 1 instruction in 1 CPU clock cycle (in its steady state):

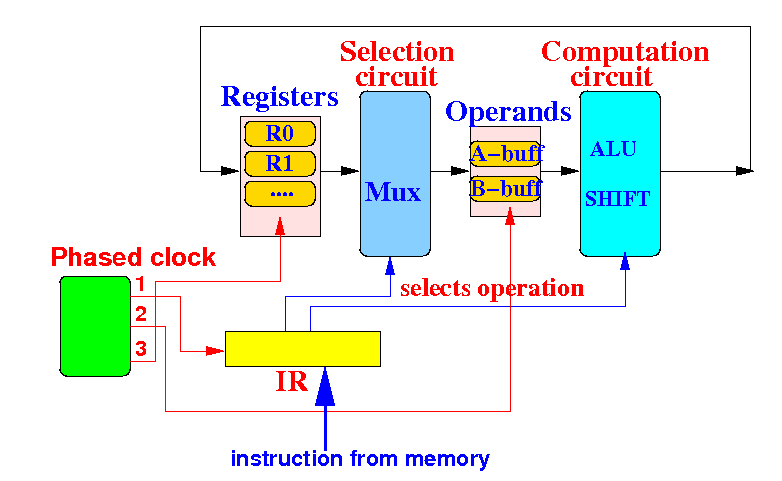

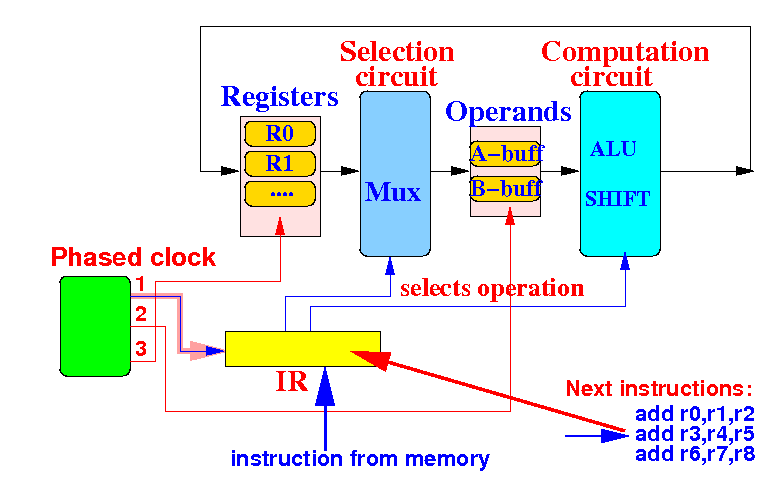

A "normal" CPU (the one that we have studied so far) operates as follows (simplified):

Let's see how the "normal" CPU executes instructions:

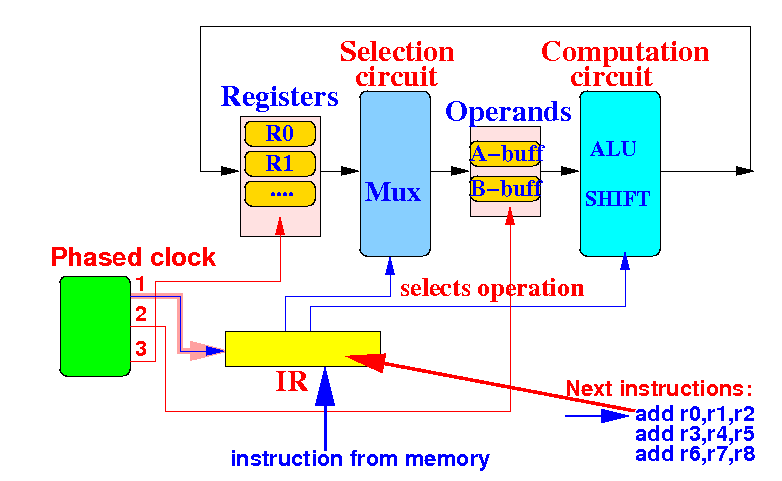

Phase 1 of clock will update IR with next instruction.

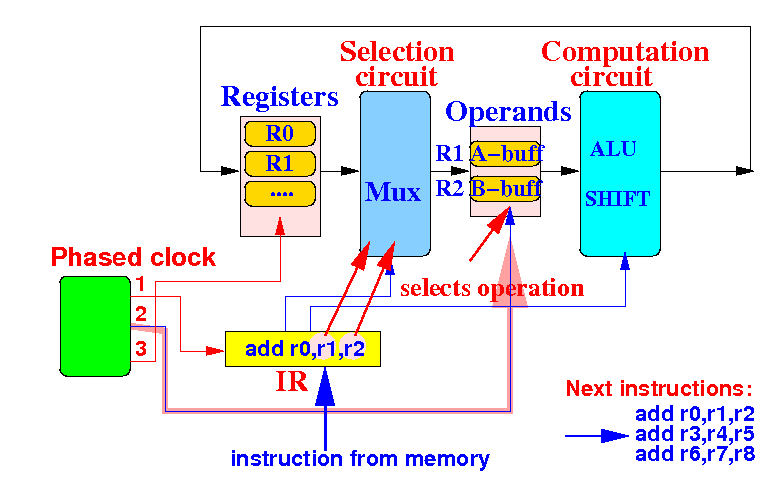

The instruction add r1,r2,r3 will fetch the operands R2 and R3:

Phase 2 of clock will update A-buffer and B-buffer with R1 and R2.

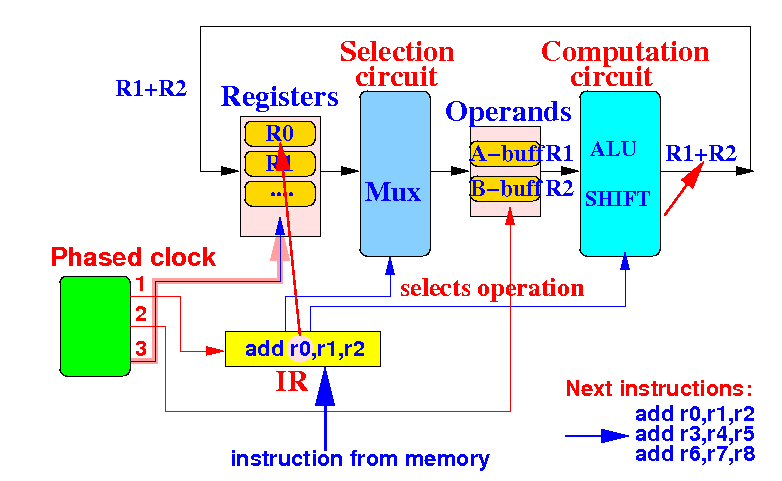

The instruction add r1,r2,r3 will then write the result into R1:

Phase 3 of clock will update R0 with R1+R2.

Then the cycle repeats:

Phase 1 of clock will

update

IR with

next instruction....

And so on

Notice:

one instruction is

executed completely

before the

next instruction

starts its

execution

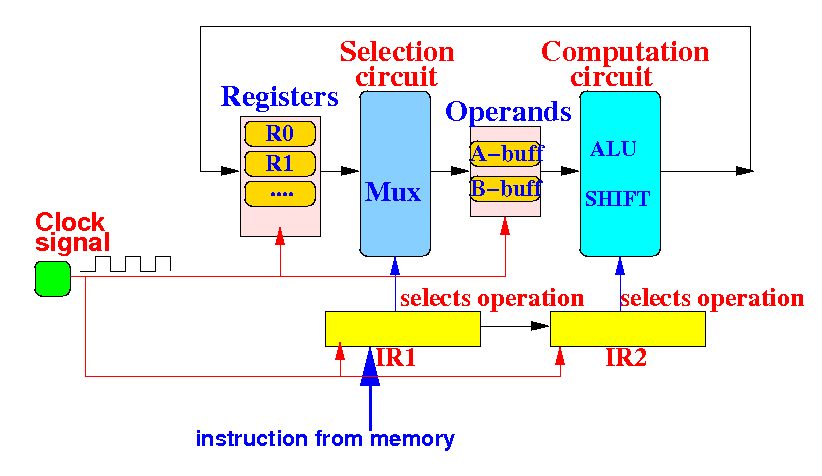

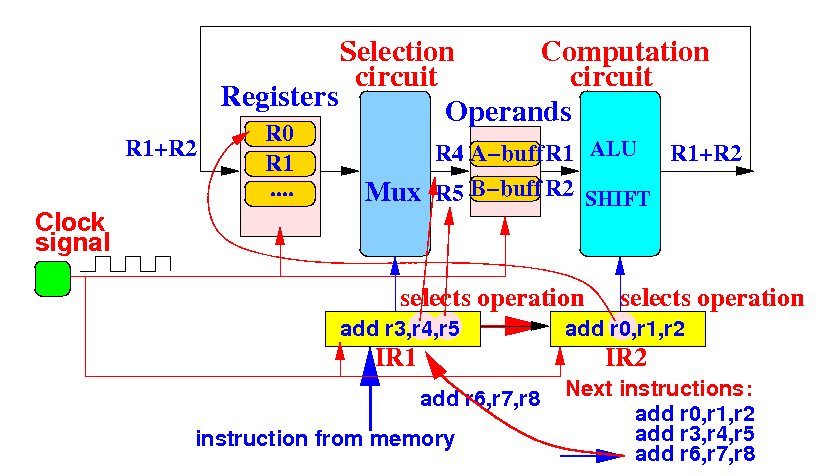

A pipelined CPU (the one that we will be studying) operates as follows (simplified):

Notice:

there are

multiple Instruction Registers

inside the

pipelined CPU !!!

Different

IRs are

controlling

a different parts (= execution phase)

of the CPU

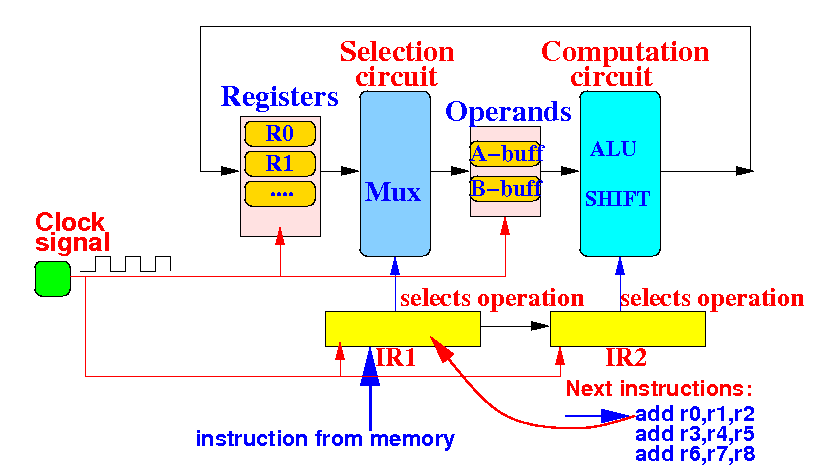

Let's see how the pipelined CPU executes instructions:

The clock will update IR1 with next instruction (and other registers too, but let's ignore them for now - assume that IR2 contains a "NOP" (= No Operation) instruction)

The instruction add r1,r2,r3 in IR1 will fetch the operands R2 and R3:

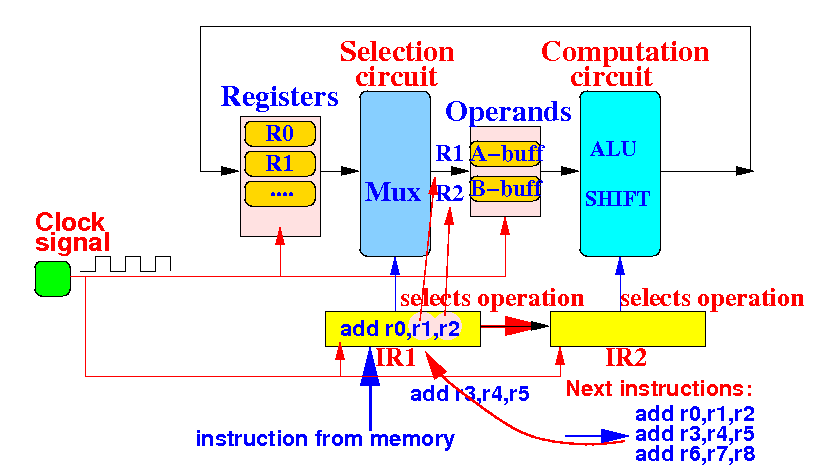

The clock will update A-buffer and B-buffer with R1 and R2 and simultaneously (1) copy IR1 to IR2 and (2) fetch next instruction into IR1 !!!

The instruction add r4,r5,r6 in IR1 will fetch the operands R5 and R6 and simultaneously instruction add r1,r2,r3 in IR2 will write the result R1+R2 into R0:

The clock will update R0 with R1+R2 and simultaneously (1) update A-buffer and B-buffer with R4 and R5 and (2) copy IR1 to IR2 and (3) fetch next instruction into IR1 !!!

|

Simplifications intorduced to make it easier to build a pipelined CPU:

|

The 3 categories of machine instructions that have similar processing requirements (i.e.: requires similar resources to execute these instructions):

|

|