|

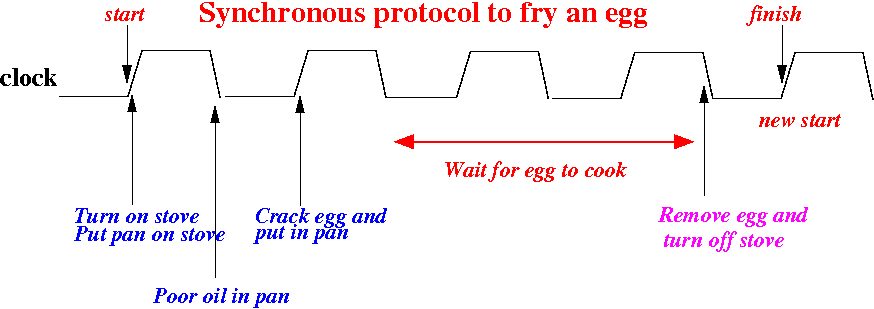

Steps to fry an egg:

|

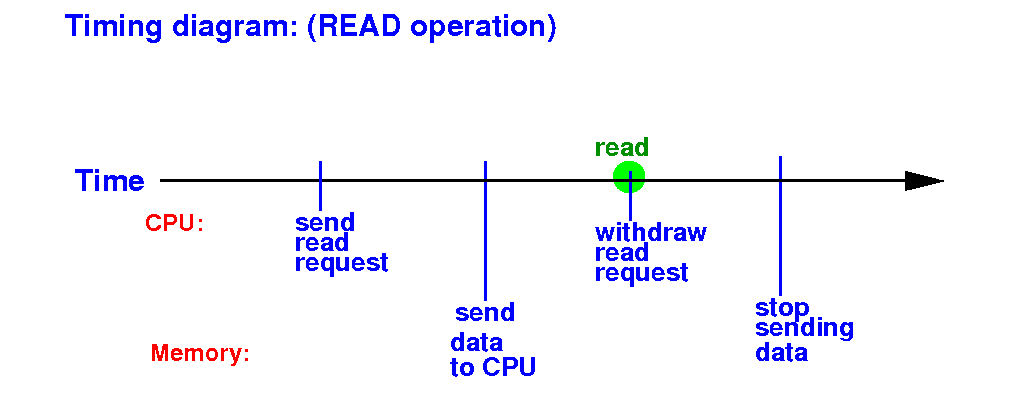

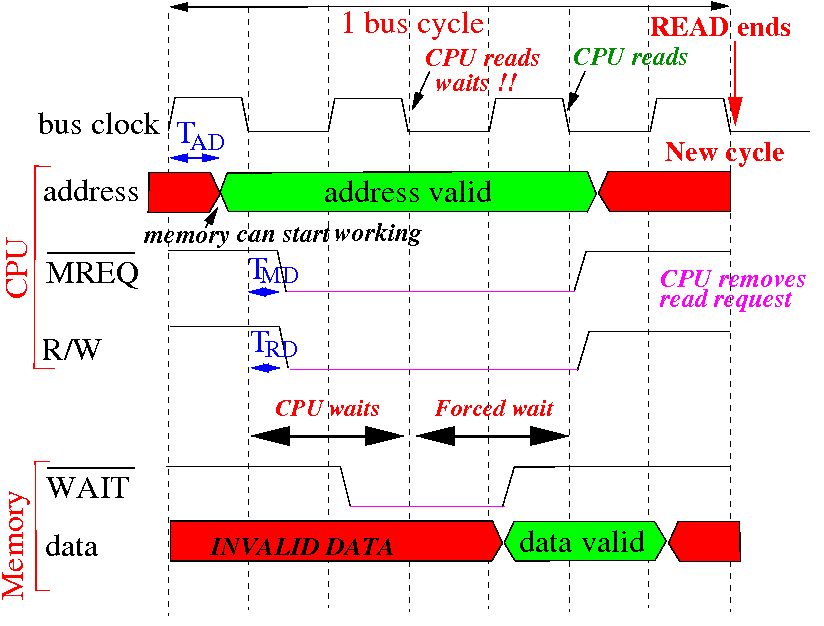

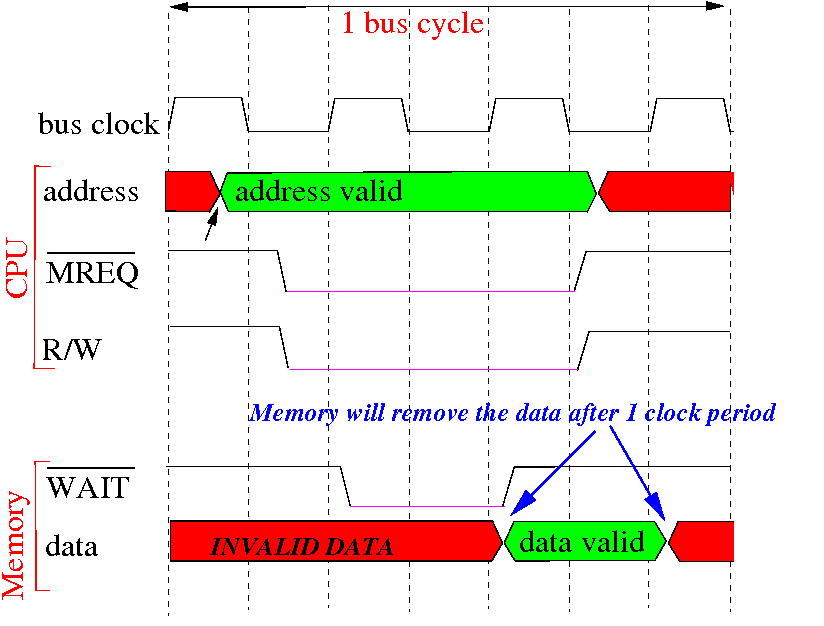

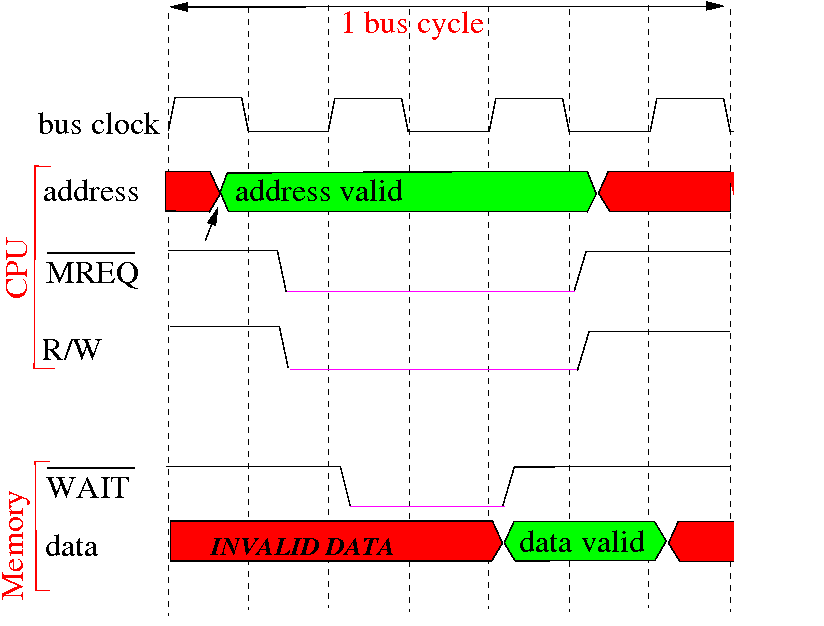

Protocol steps exchanged between the CPU and the memory in a READ operation:

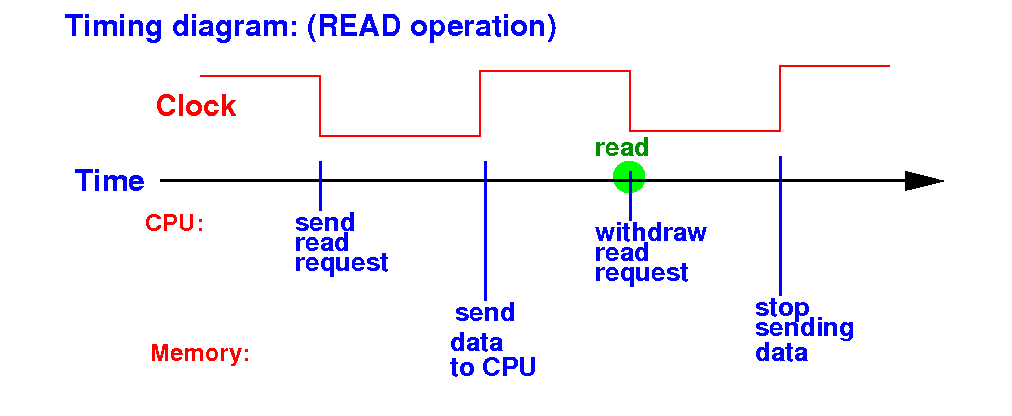

In a synchronous protocol, the protocol steps are driven (= scheduled) by a clock signal:

The protocol steps are scheduled chronological at the rise or falling edges of the clock:

I will explain the timing diagram in a piece meal manner next....

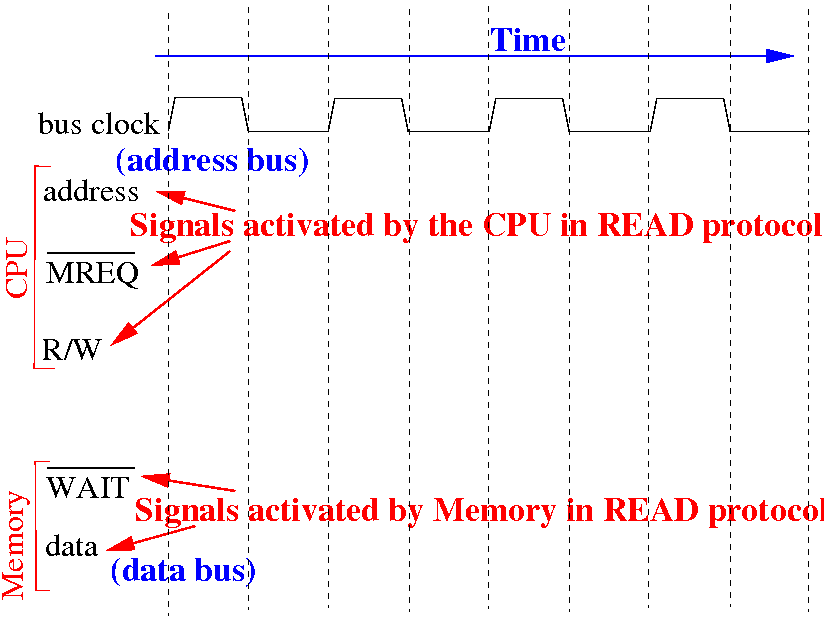

The signals activated by the CPU and memory when executing the sync READ procotol are:

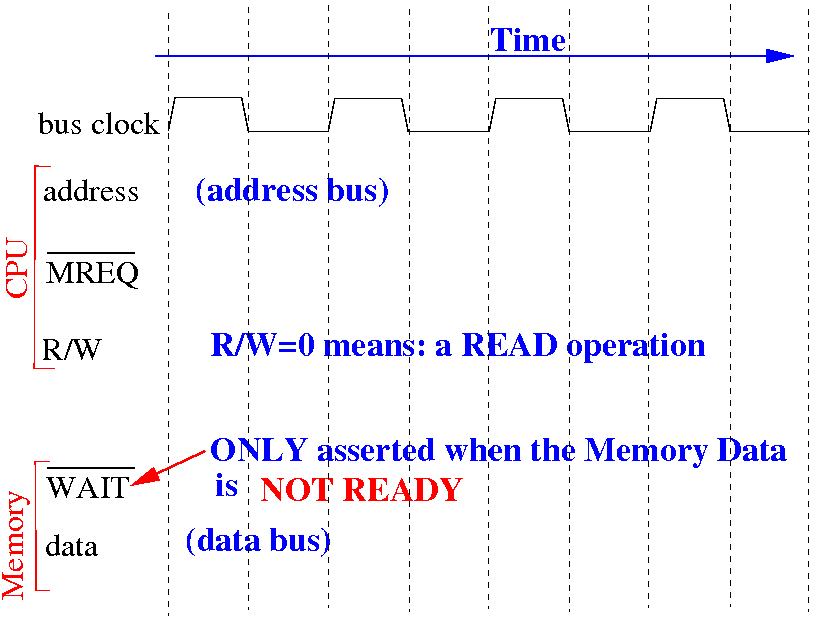

The meaning of the signal transitions in a timing diagram:

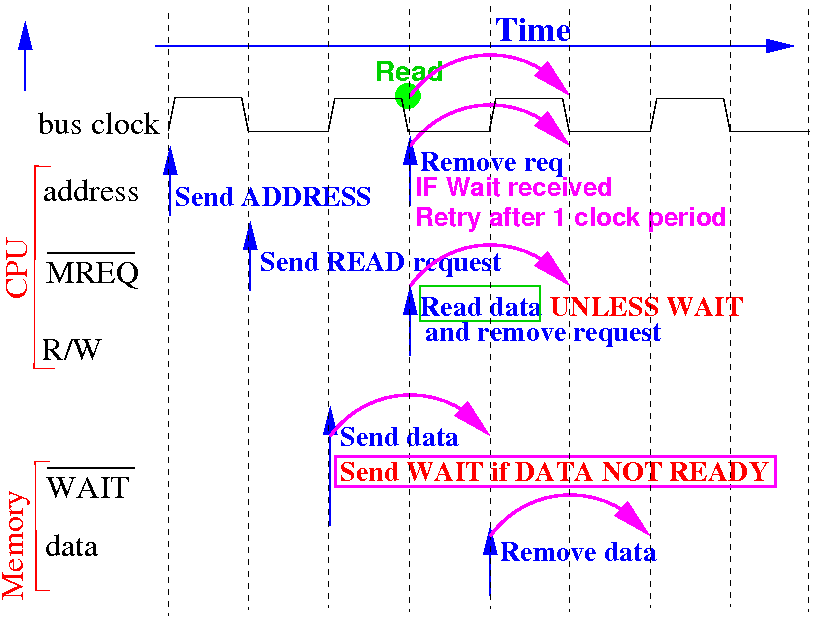

A (possible) schedule (= timing) of the protocol events using the clock signal:

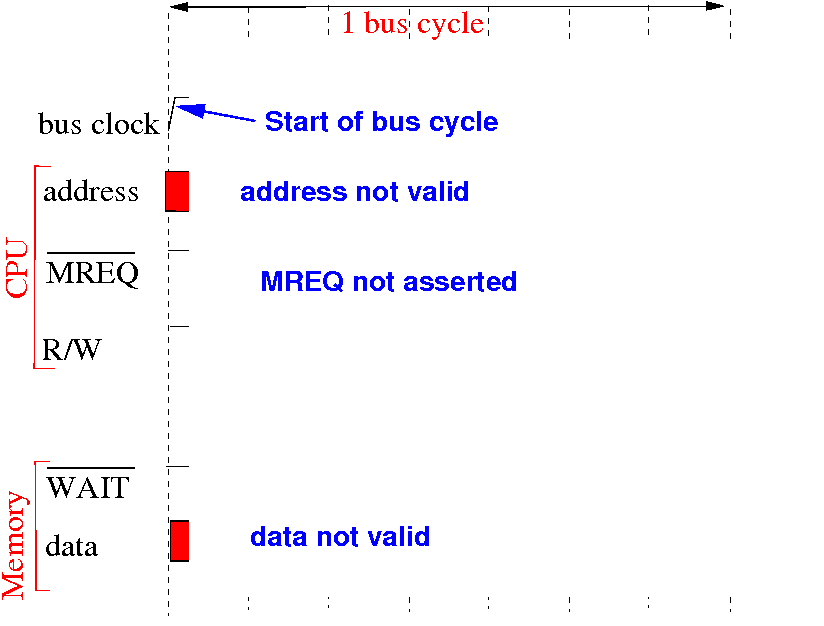

The signals at The start of an synchronous READ protocol are as follows:

The CPU now starts a READ operation and runs the sync READ protocol...

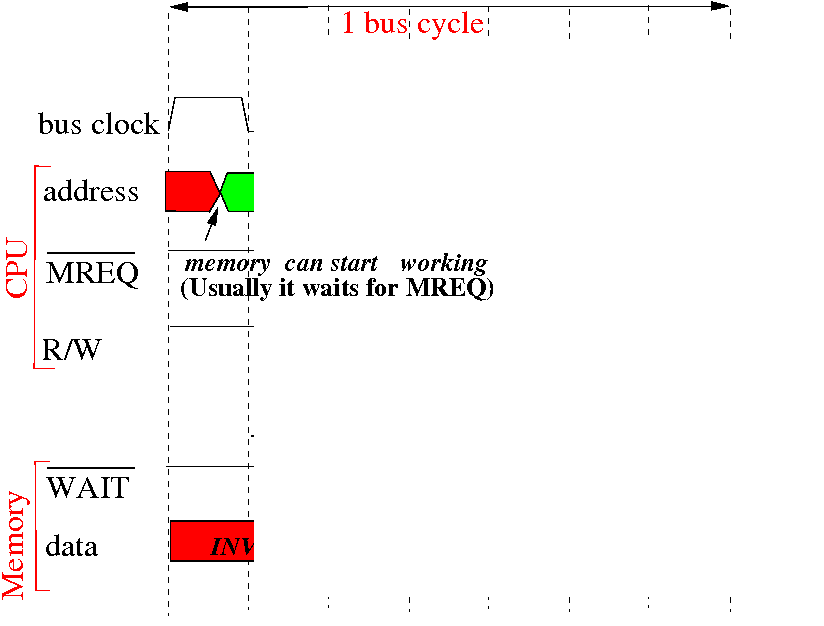

(1) the CPU sends out the address :

The memory may start working on the request; but it will usually wait till the next step...

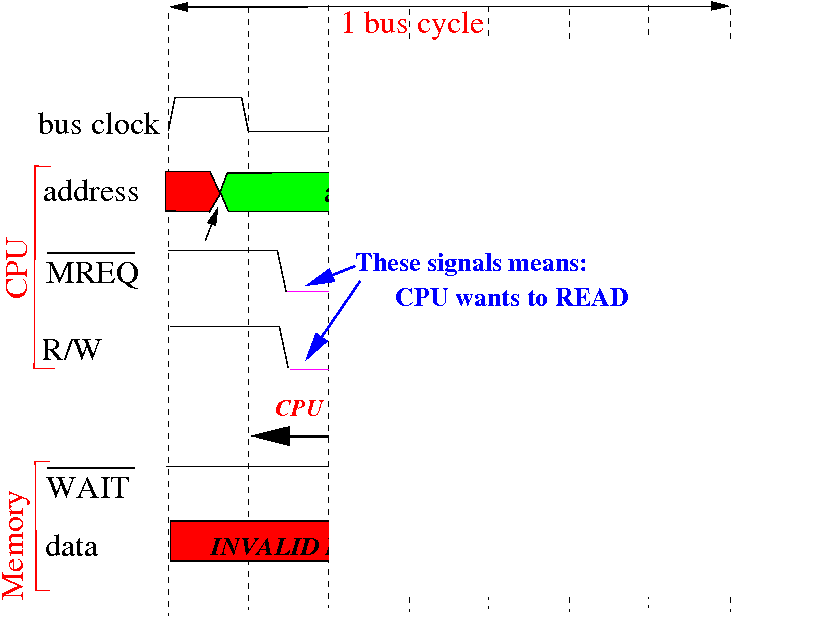

(2) the CPU sends out the READ request:

The memory will now fetch the data requested in the READ operation...

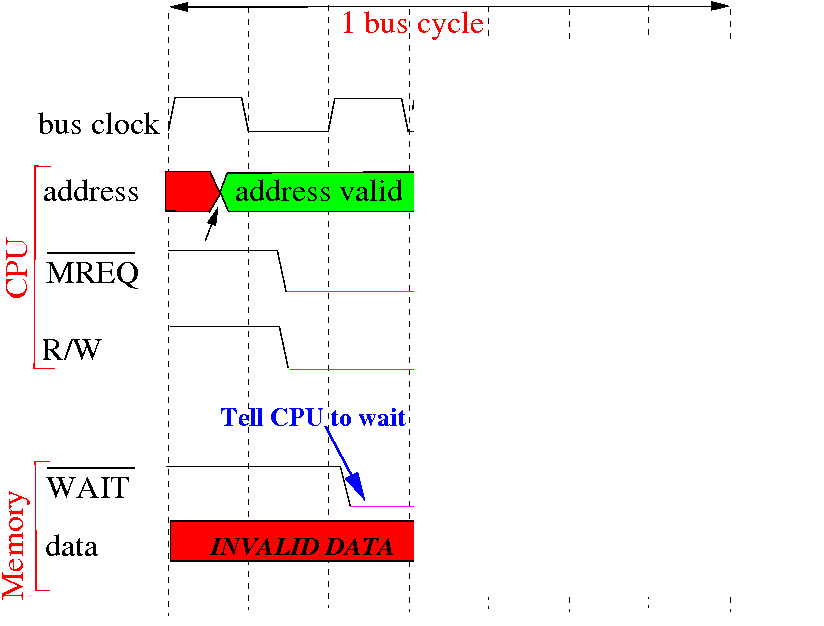

(3) the memory will now process the READ request:

The slower working memory will usually asserts the WAIT signal to prevent the CPU from reading invalid data on the data bus. A fast memory do not assert WAIT.

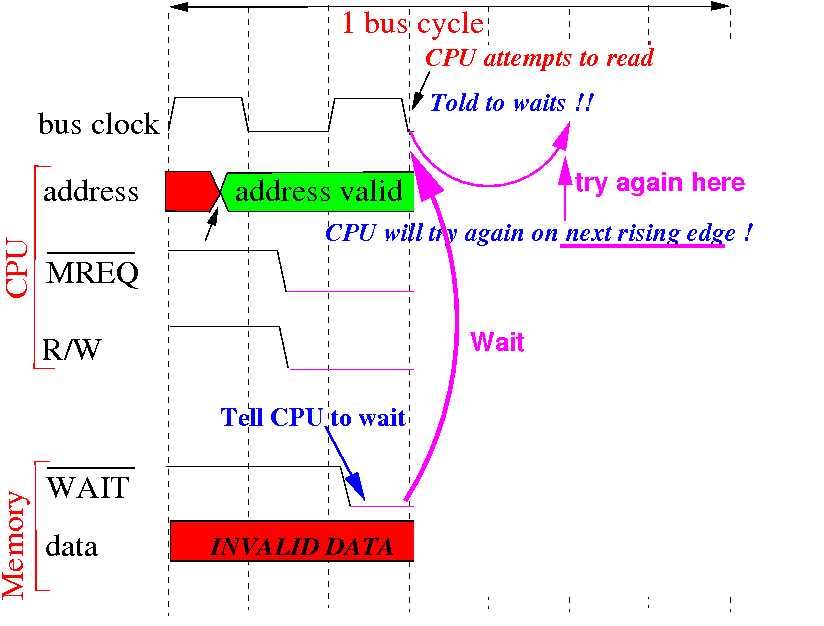

(4) the CPU attempts to read on the falling clock edge and stopped by the WAIT signal:

The CPU will try again at the next falling clock edge !!

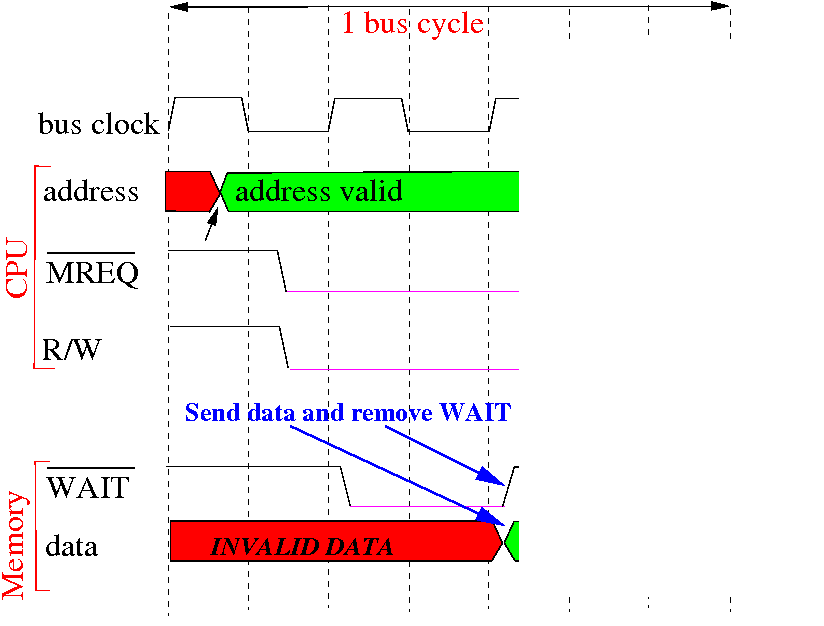

(5) the memory finally sends out the data and it also removes (de-asserts) the the WAIT signal:

The Memory is done (it signals that the CPU should read the data on next falling edge !!)

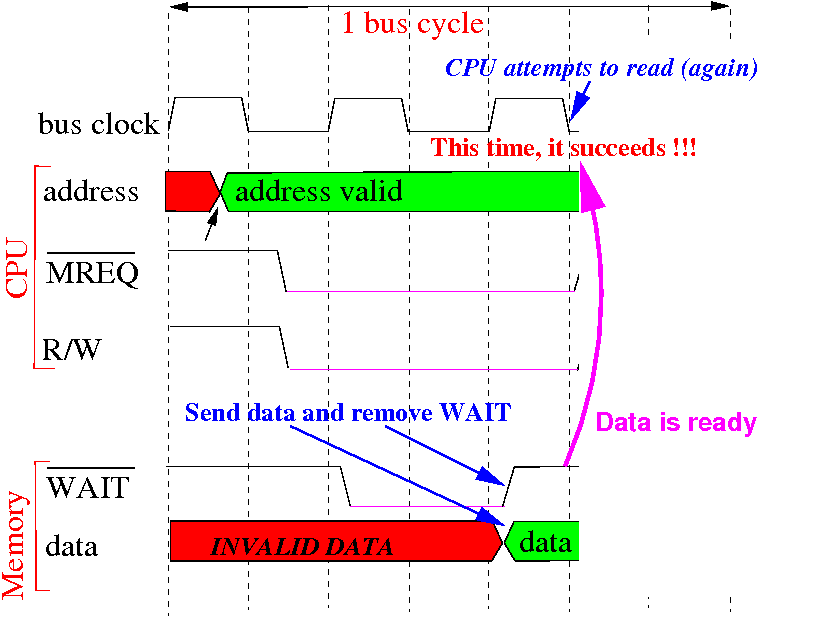

(6) the CPU attempts to READ again, and this time, the CPU succeeds:

Note that the protocol can guarantee that the data on the data bus is correct !!

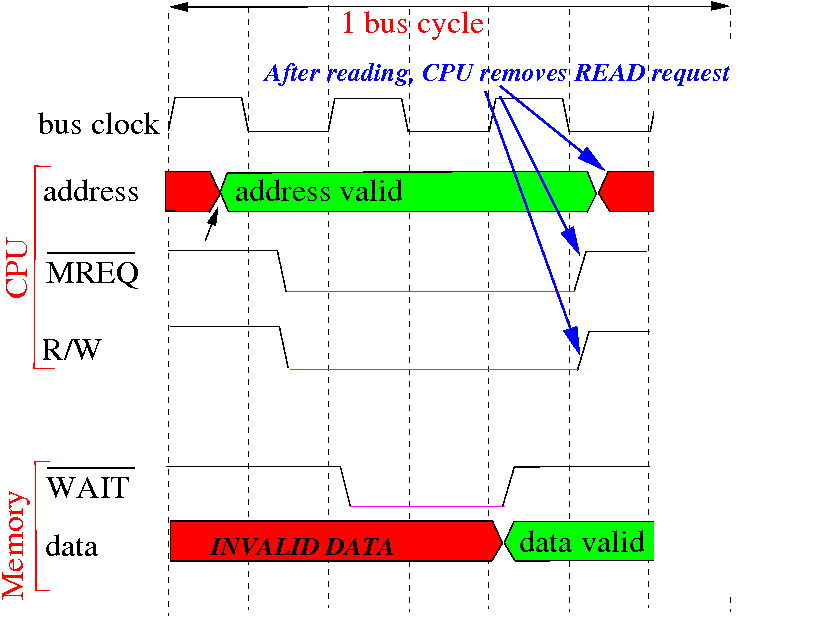

(7) the CPU must remove (withdraw) the READ request from the bus:

Unlike the asynchronous protocol, the CPU can withdraw all signals (because the memory expects the CPU to finish)

(8) the memory will remove (withdraw) the DATA response from the bus after 1 clock period:

The protocol is finished !!!

Notice that: all signals have returned to their original state !!

Therefore: a new bus cycle can start immediately !!!

|