|

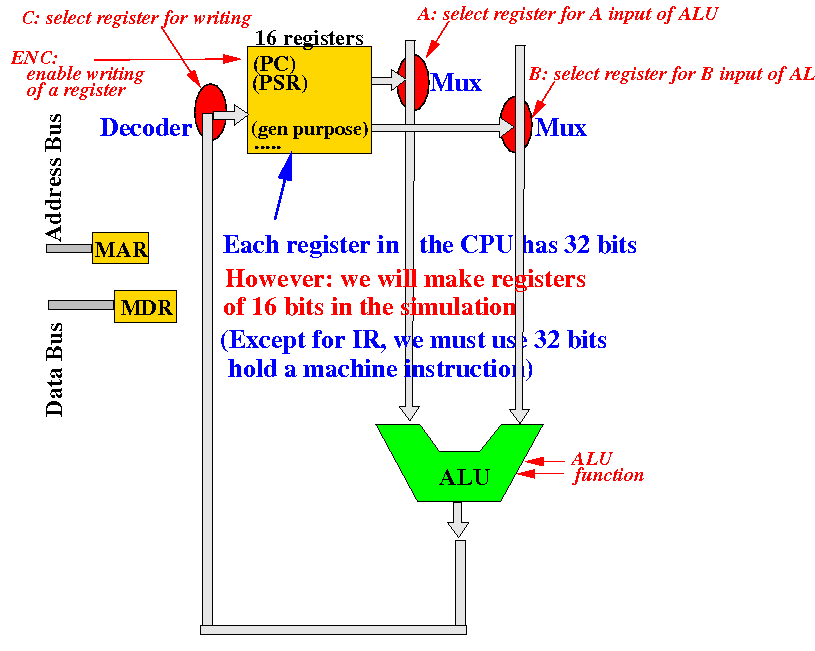

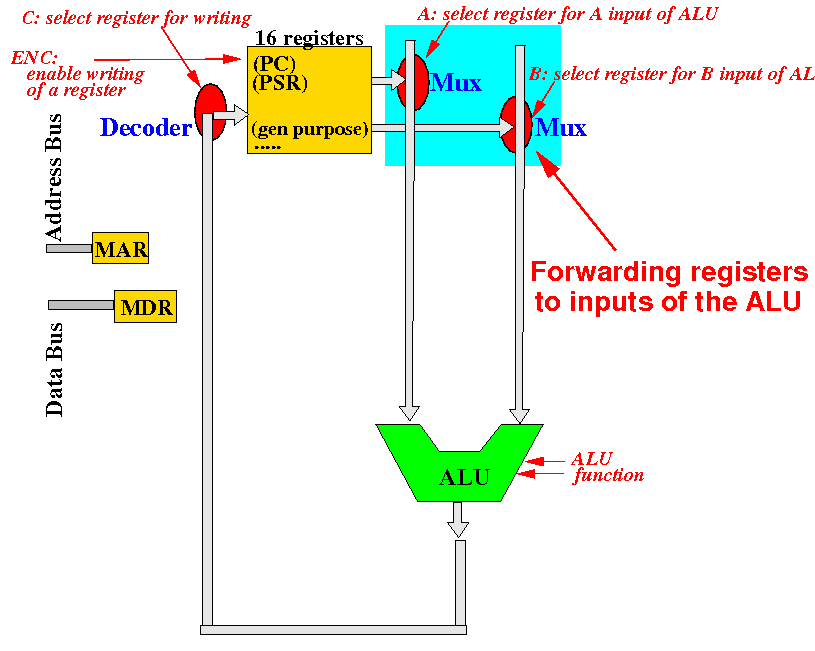

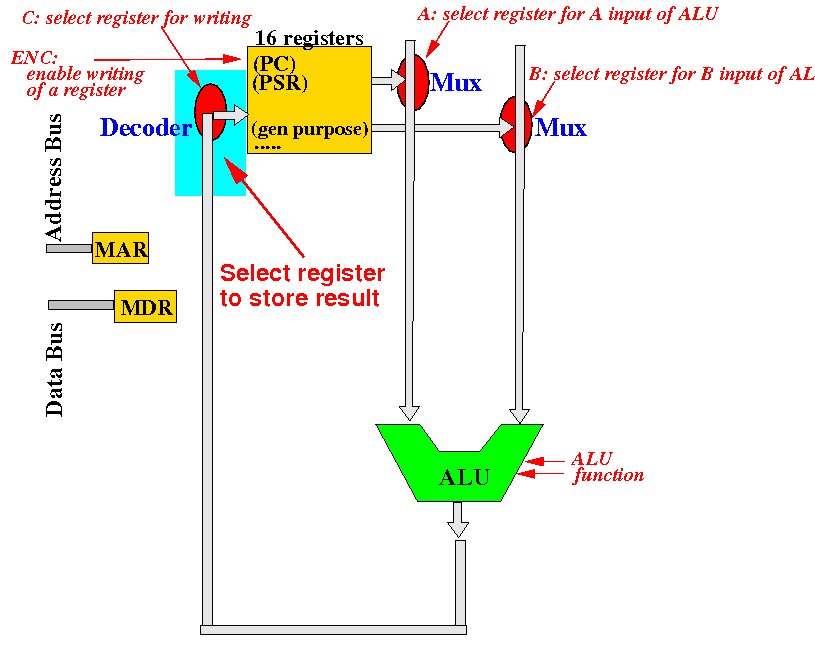

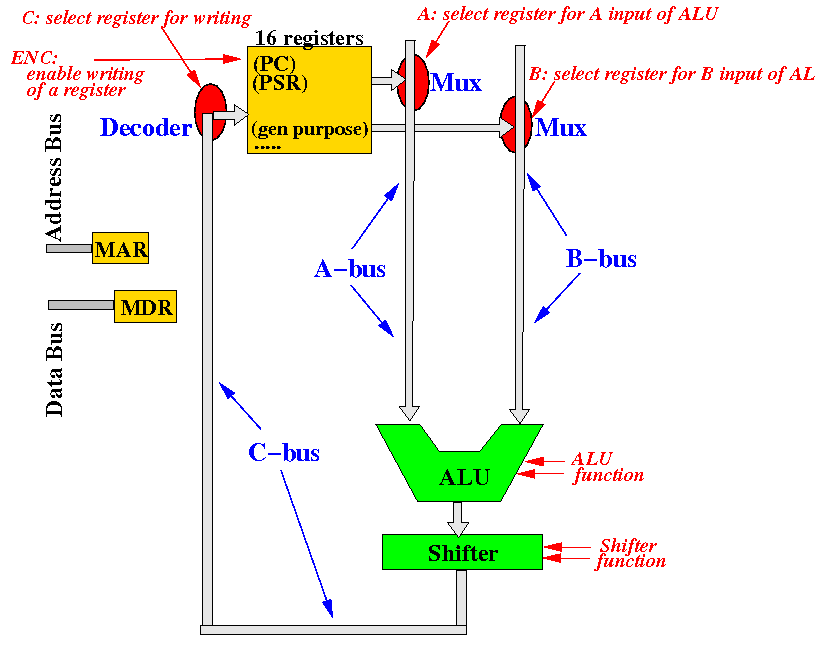

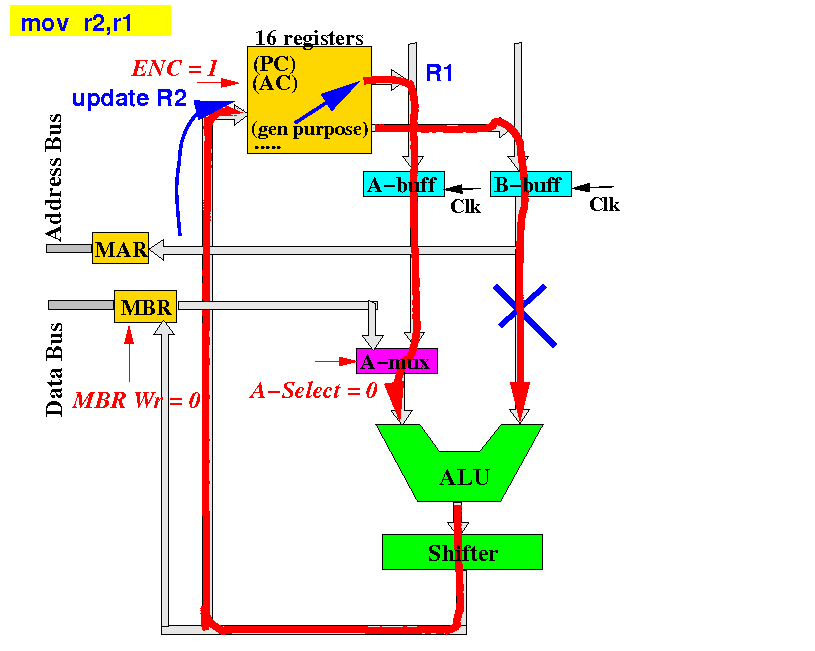

(1) How to

forward source

registers to the

ALU

(2) How to

select a

register to

update with the

output of the

ALU

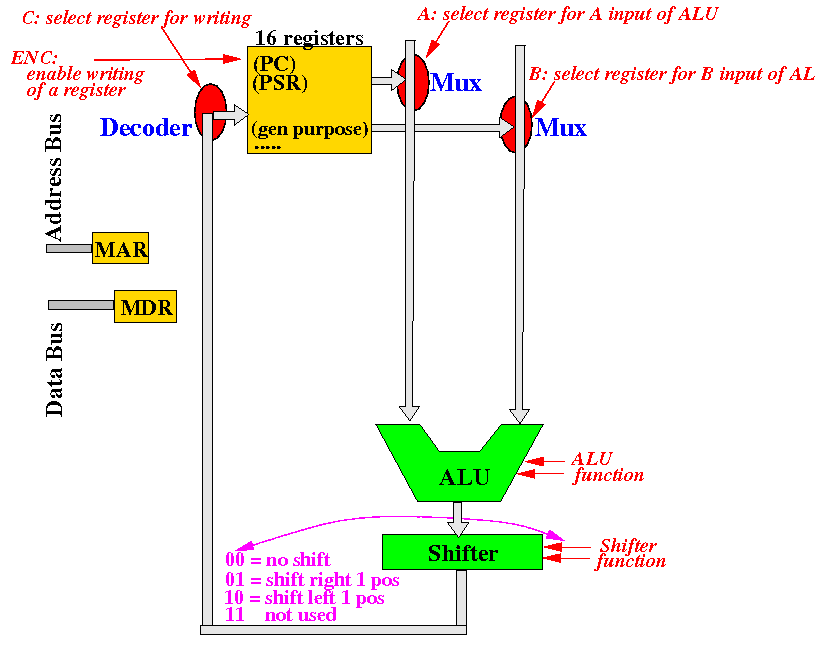

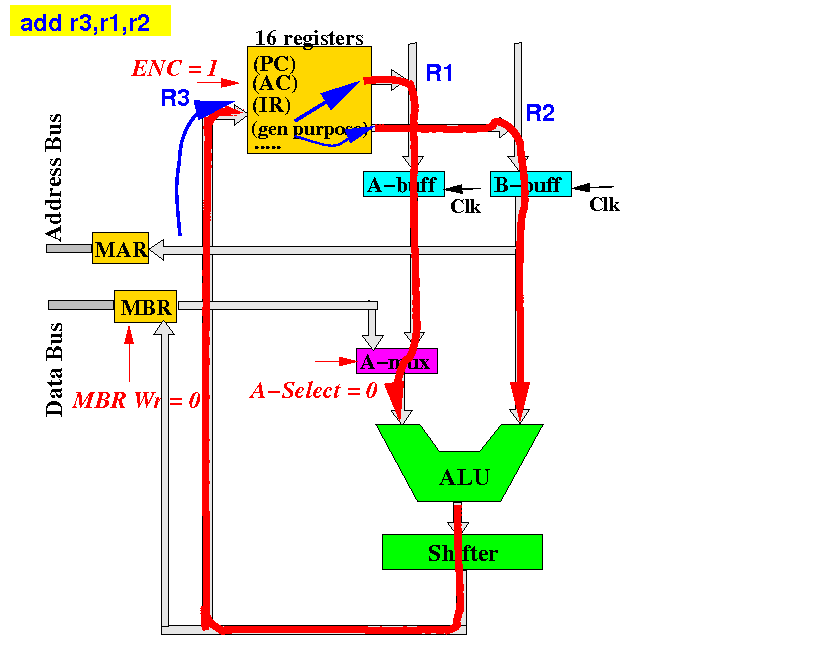

(1) How to

forward source

registers to the

ALU

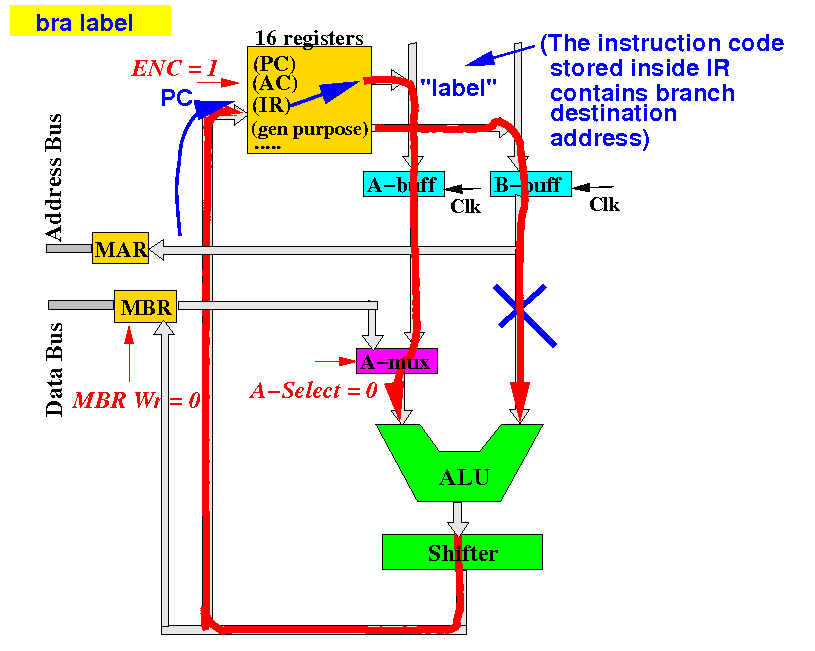

(1) How to

forward source

registers to the

ALU

(2) How to

select a

register to

update with the

output of the

ALU

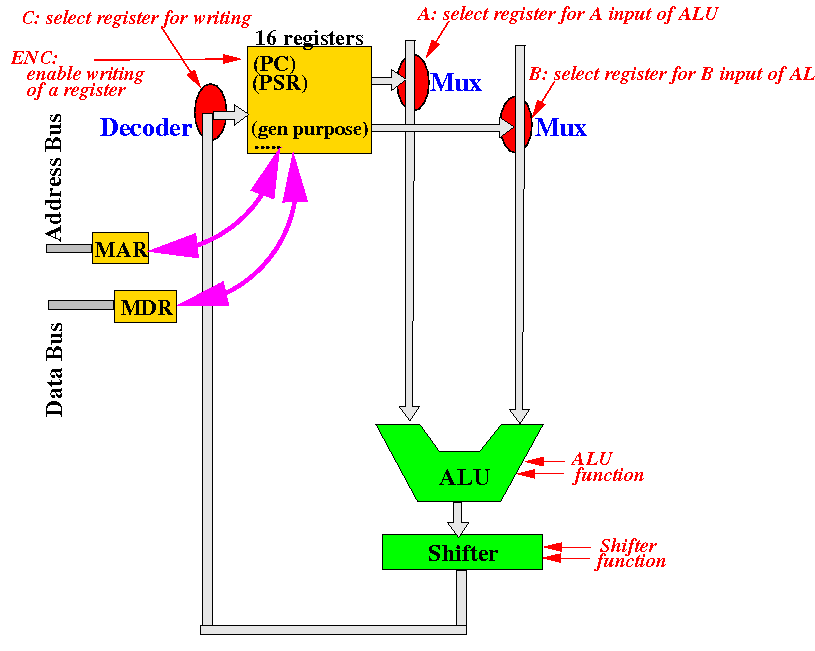

(2) How to

select a

register to

update with the

output of the

ALU

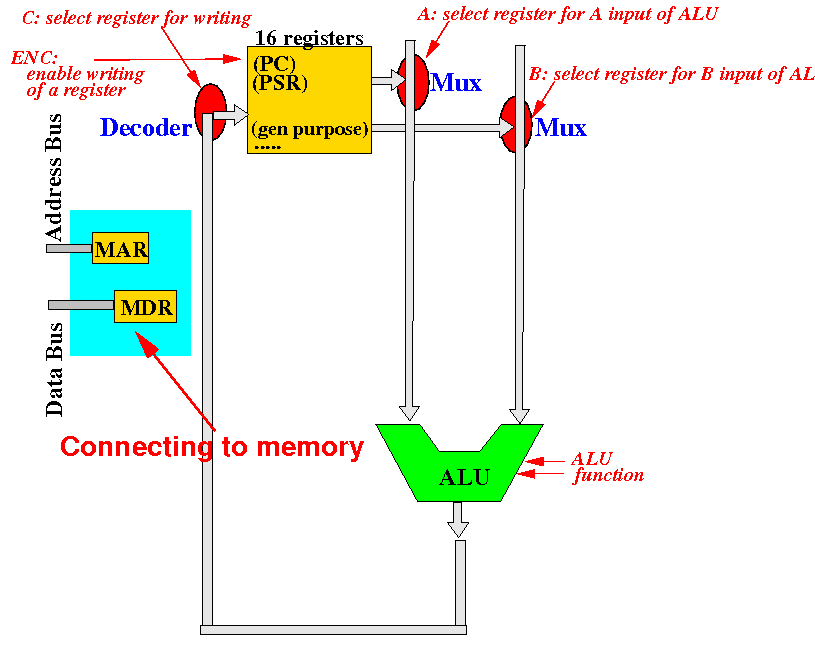

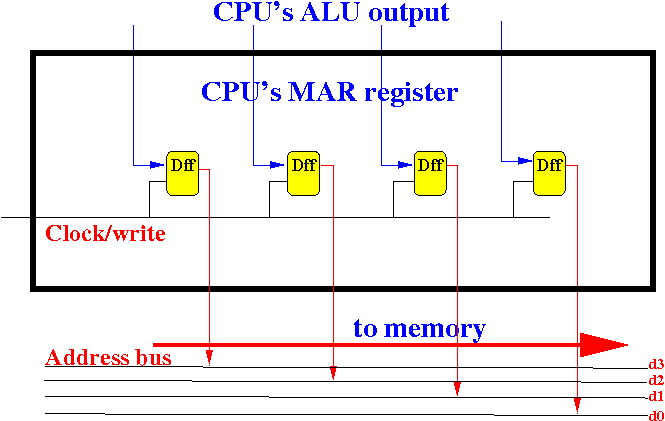

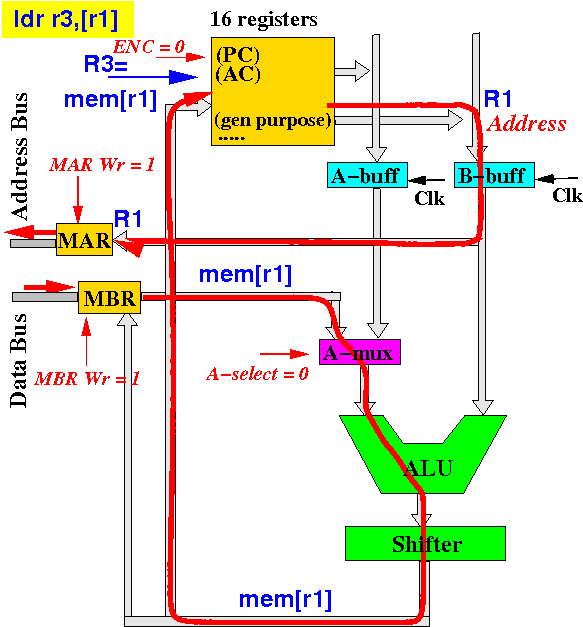

(3) How to

connect the

MAR register to the

address bus

(4) How to

connect the

MDR register to the

data bus

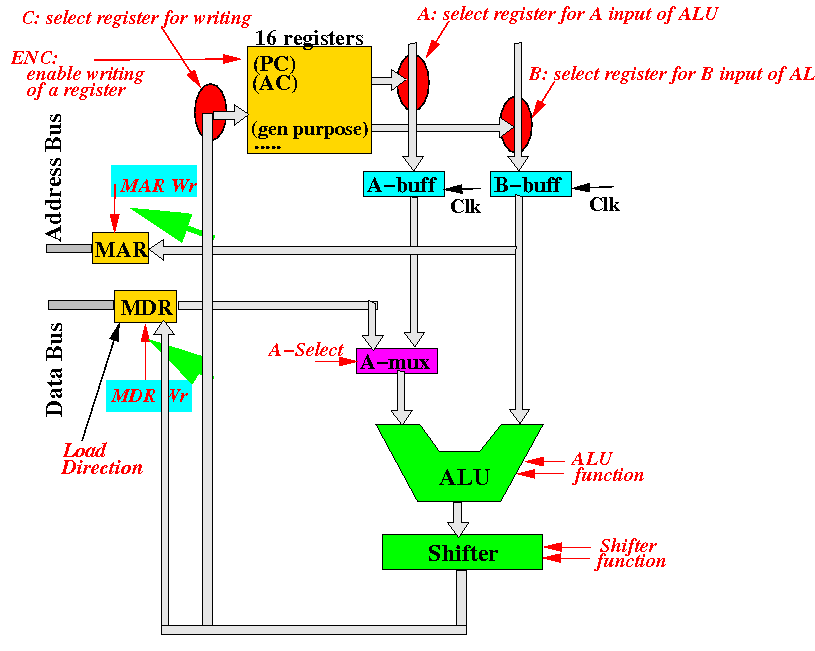

(3) How to

connect the

MAR register to the

address bus

(4) How to

connect the

MDR register to the

data bus

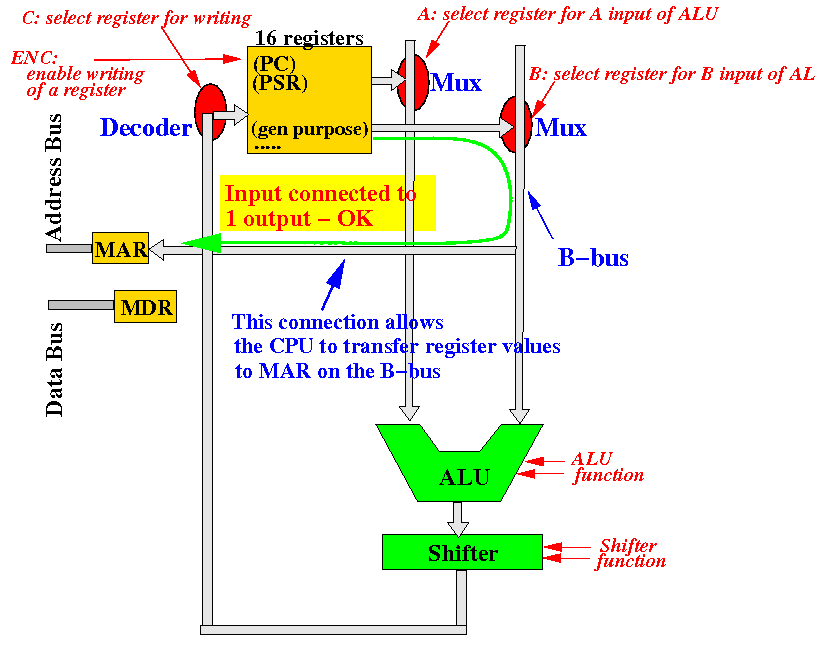

For convenience sake, we call the following buses: the A-bus, the B-bus and the C-bus:

(1) We first add a shifter circuit after the ALU to shift the ALU output left or right:

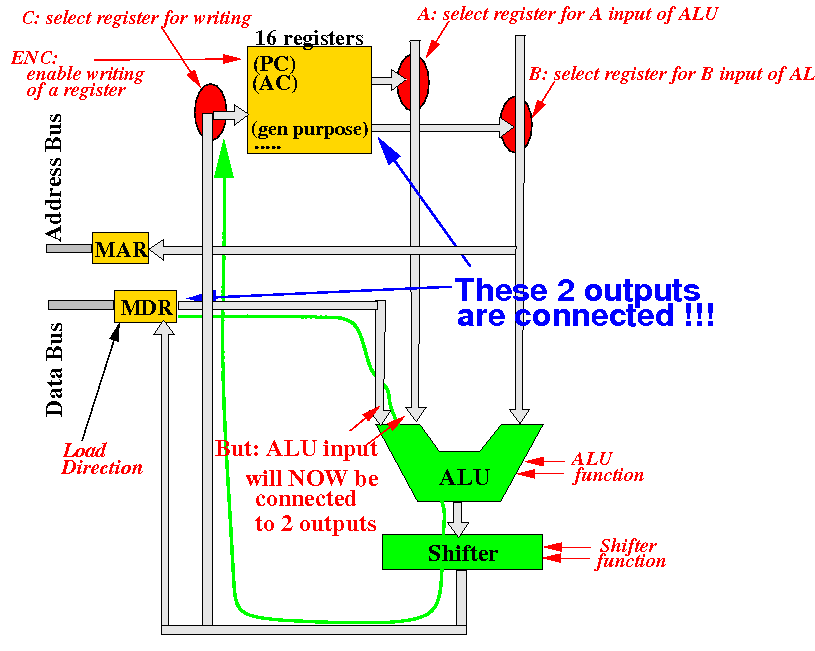

Notice that: there are no paths connecting the MAR and MDR registers and the other CPU registers:

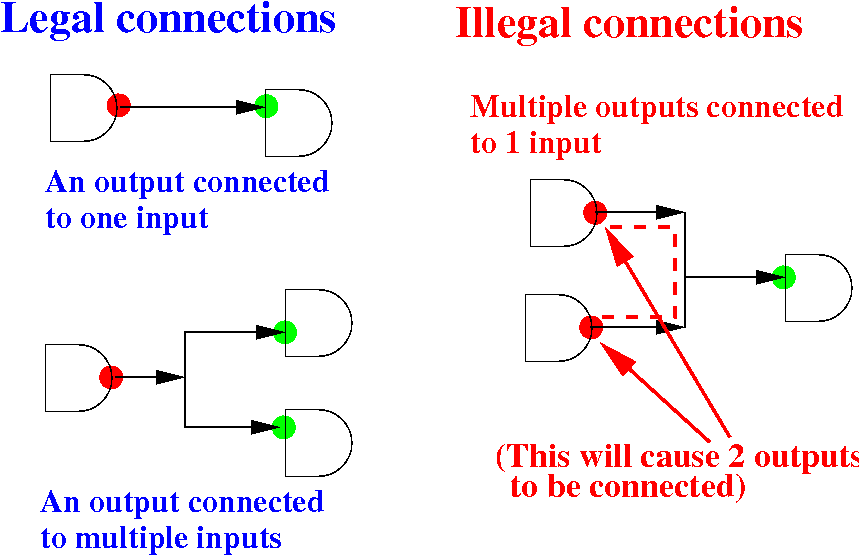

Review: you cannot connect 2 outputs with each other

Note: later in the course, you will learn about a "high impedance" output circuit that can be connected together.

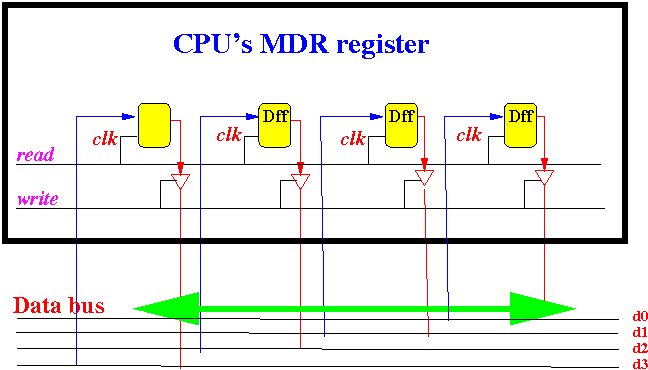

(2) We connect the B-bus to the inputs of the MDR:

This will allow the CPU to transfer an address from a register to the MAR in the ldr and str instructions

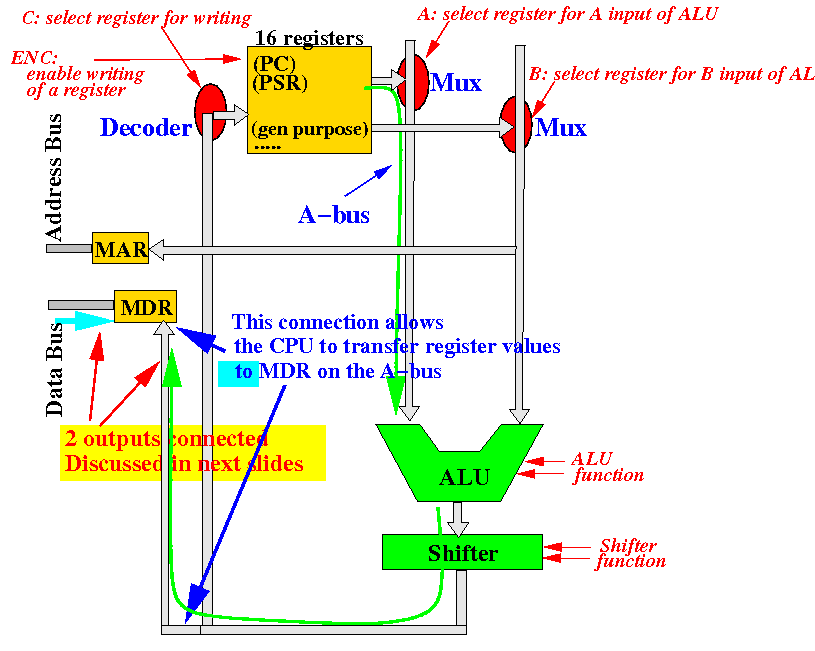

(3) We connect the C-bus to the inputs of the MDR:

This will allow the CPU to transfer data from a register to the MDR in the str instructions

(4) We connect the MDR to the inputs of the ALU:

This will allow the CPU to transfer data from the MDR to a register in the ldr instructions

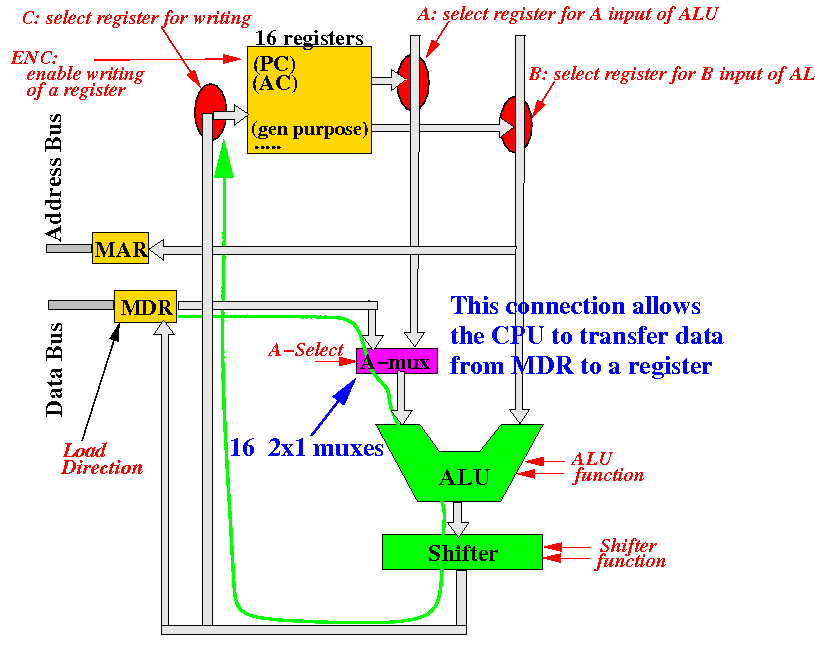

(4) Unfortunately, we cannot connect the MDR outputs directly to the ALU inputs:

Because this will connect the outputs of the MDR to the outputs of a register !

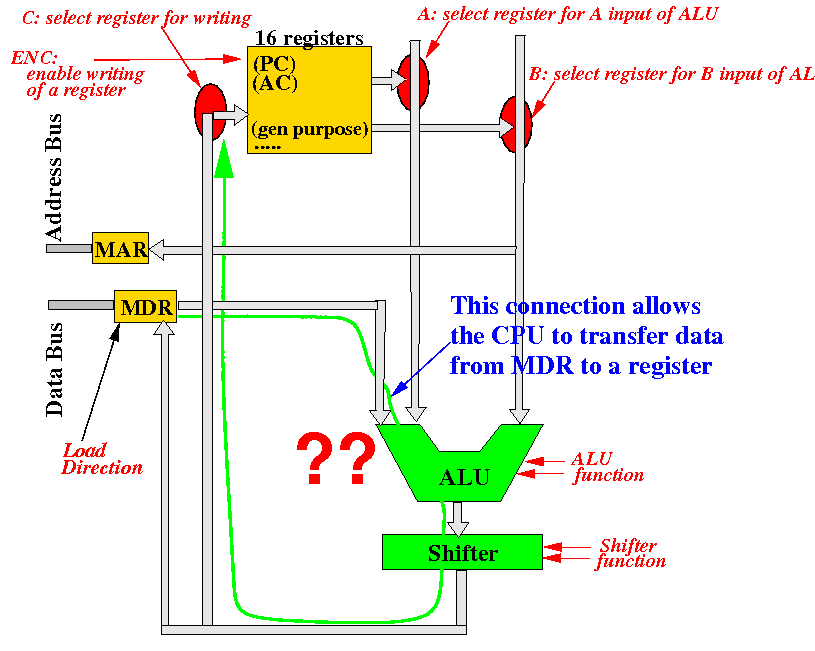

(4) Solution: we use a 2 way multiplexor to switch between the register outputs and the MDR outputs:

The A-Select signal is used to choose between the A-bus data and the MDR data

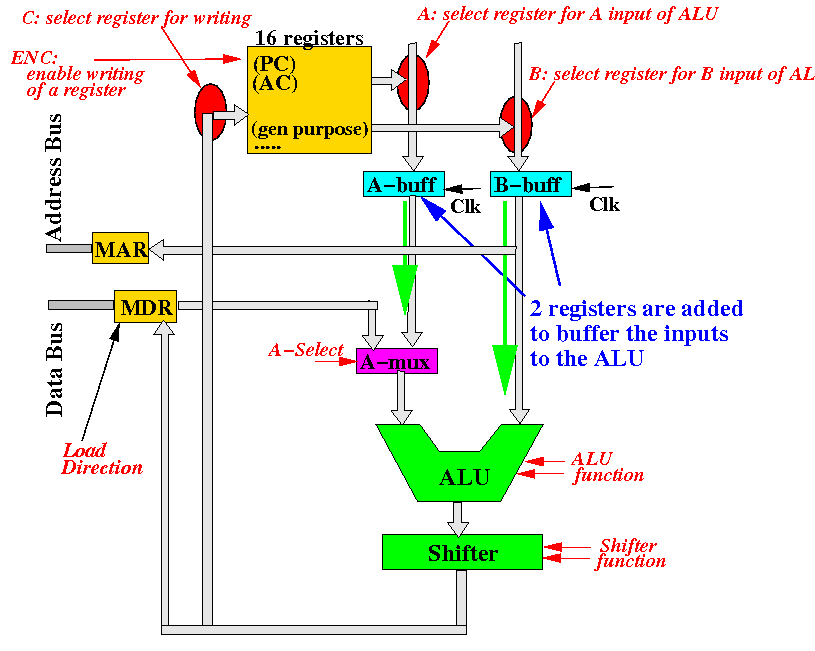

(5) The registers A-buffer and B-buffer are added on the A-bus and B-bus to simplify timing:

The timing problem in the event sequencing problem will be discussed later...

Note: all registers (MAR, MBR, A-buffer and B-buffer) has an associated write signal

Catagory 1: Move: mov, movw, movt Arithmetic: add, sub, mul, cmp Branching: b, bgt, bge, blt, blt, beq, bne Catagory 2: Load: ldr r1, [r2] Store: str r1, [r2] |

I will now show you the pathways in the CPU used to transfer data in the execution of each of these types instructions

The mov, add/sub/... and branch instructions uses this pathway:

The mov, add/sub/... and branch instructions uses this pathway:

The mov, add/sub/... and branch instructions uses this pathway:

The only difference is the branch instruction updates the Program Counter PC

A ldr instruction uses this pathway:

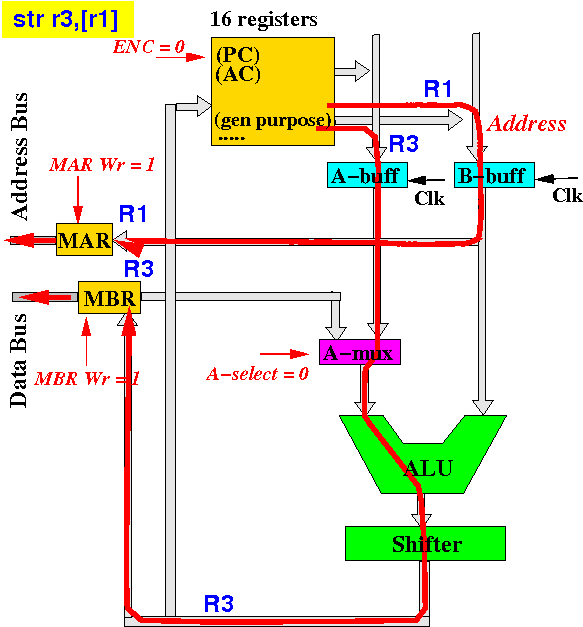

A str instruction uses this pathway: