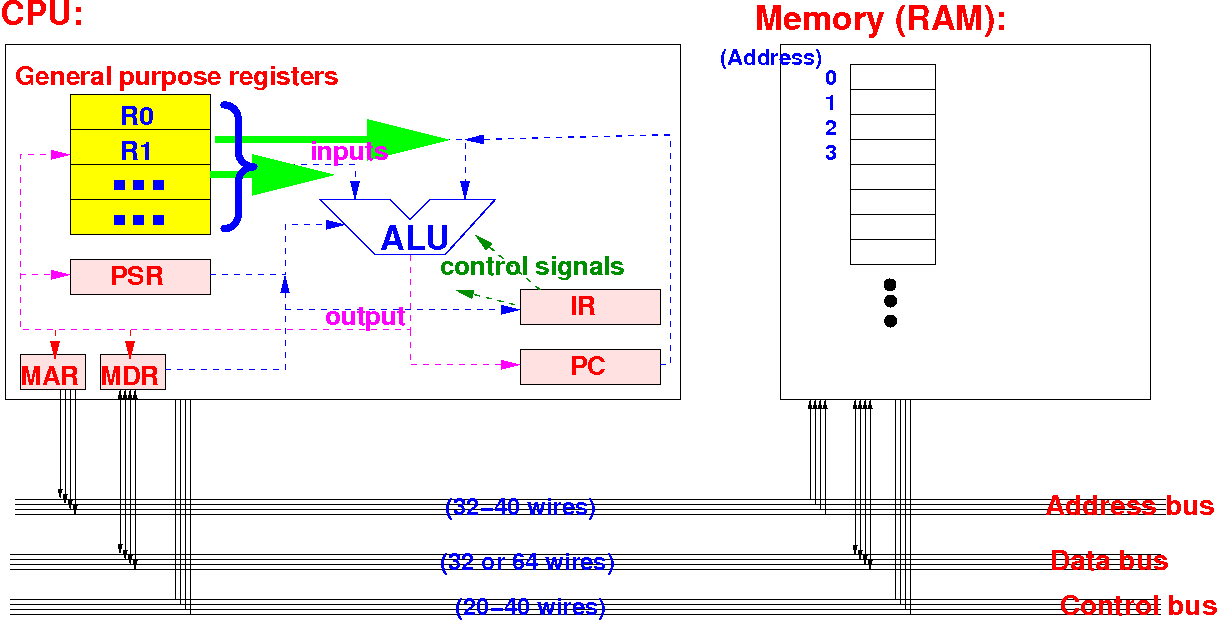

We have now studied various parts of the CPU:

We have studied how to forward the operands from the registers to the inputs of the ALU:

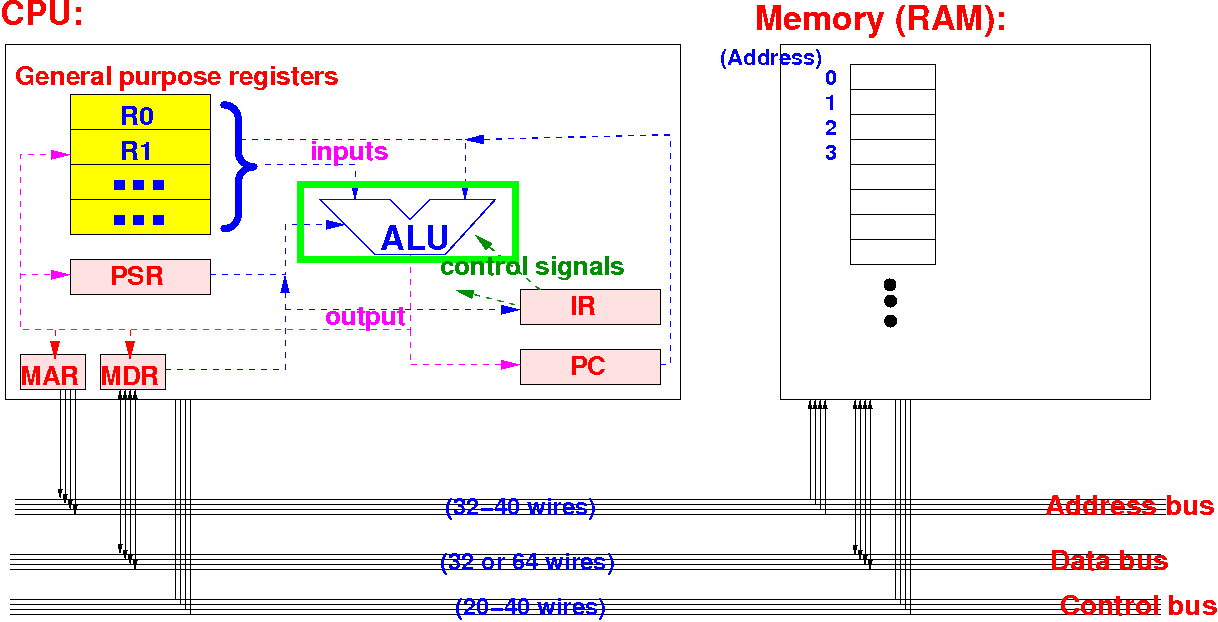

We have studied how a (simple) ALU works:

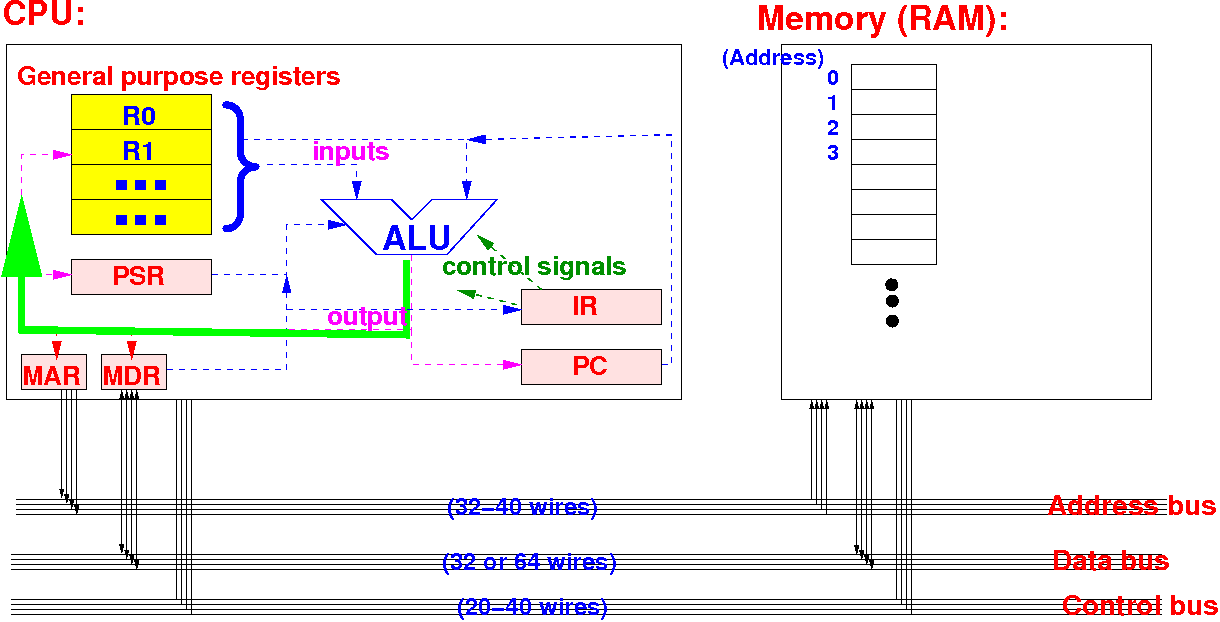

We have studied how to forward the result from the ALU output to the registers (for storage):

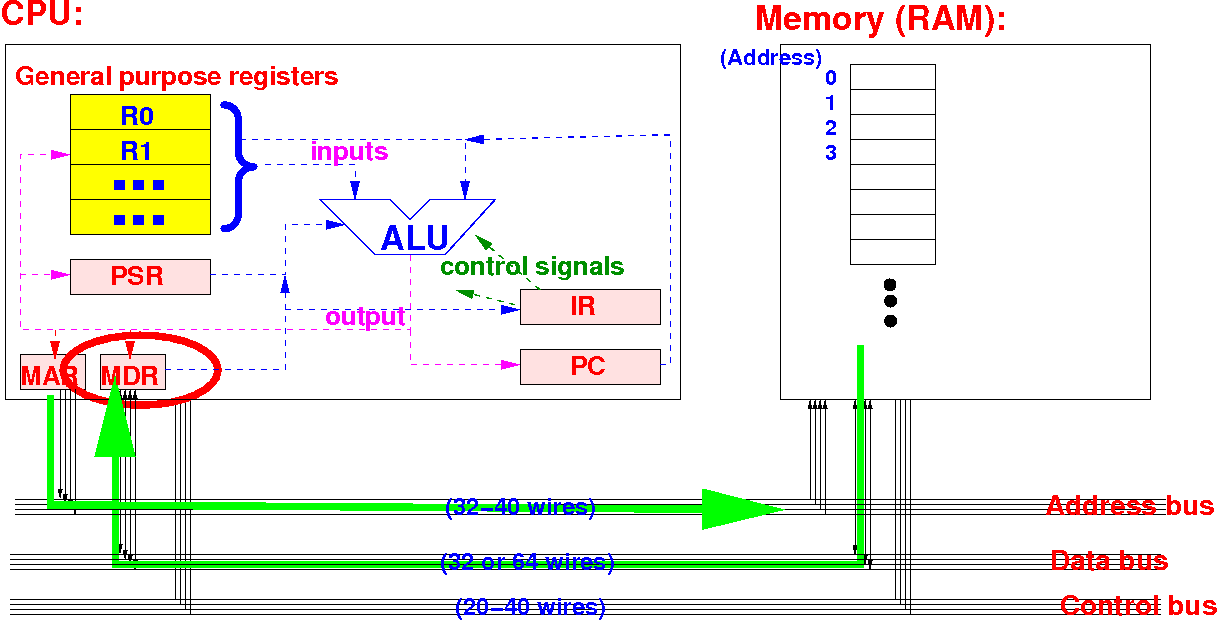

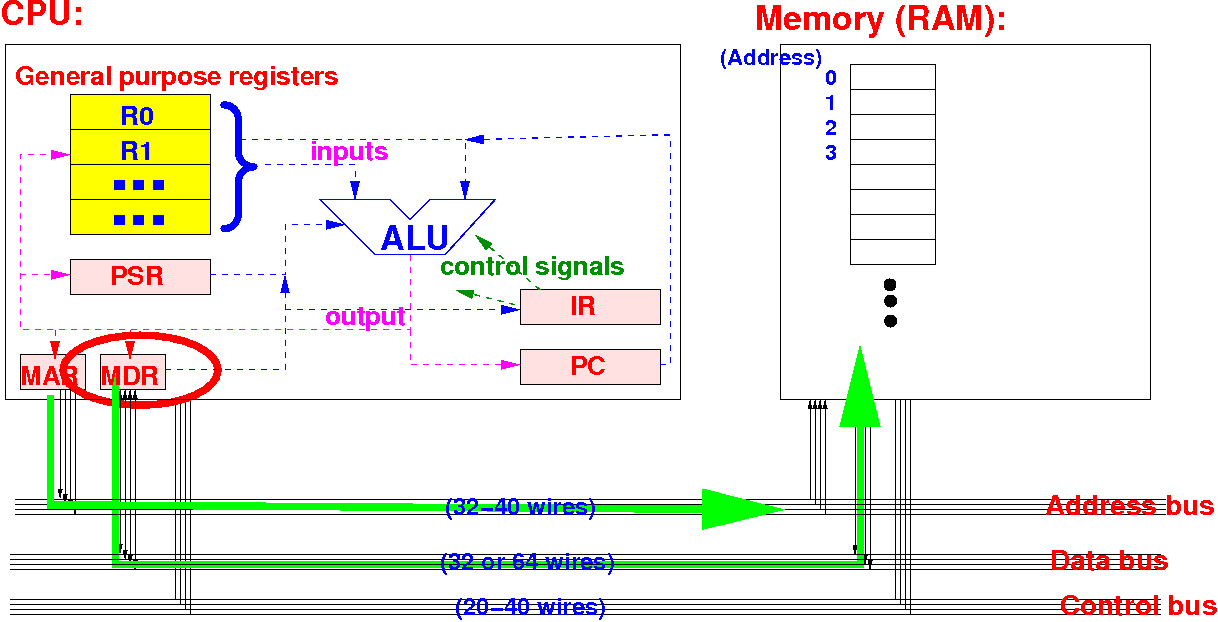

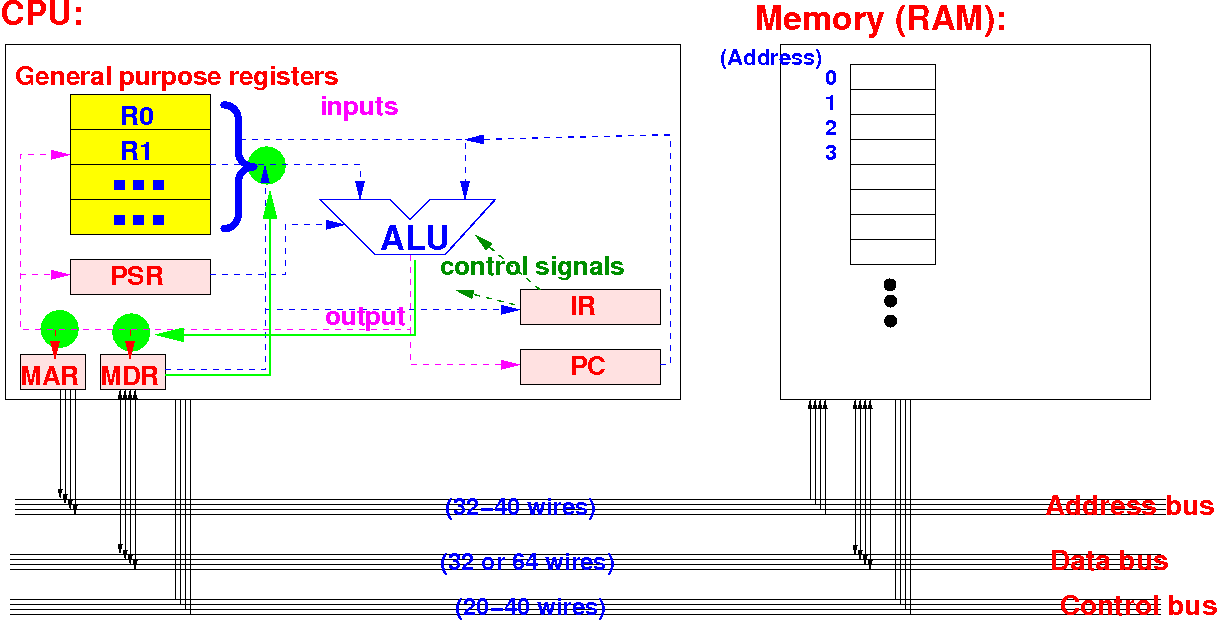

We have studied how the CPU transfer data from the memory to its MDR register:

We have studied how the CPU transfer data from its MDR register to the memory:

|

The basic types of instructions that the CPU (= computer) can execute are:

|

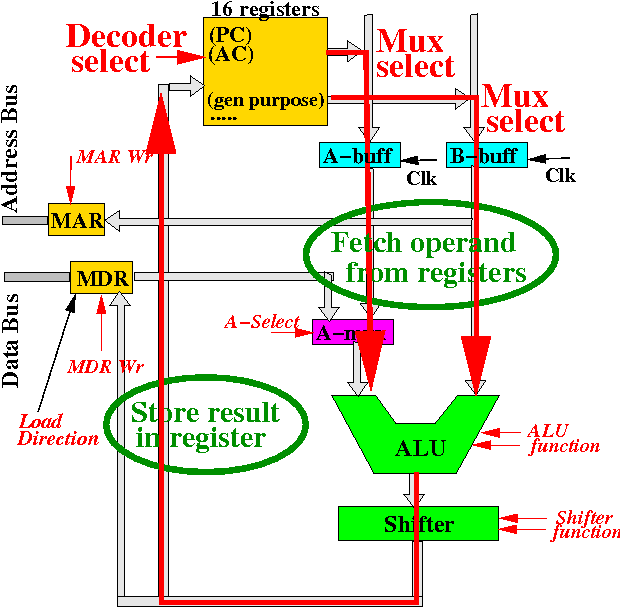

We will need to create new path ways in the CPU to connect the registers to the MAR and the MDR:

The new paths (routes), are created by adding multiplexors !!!

There is a network of pathways inside the CPU used to route (binary) data:

This pathway makes it possible transfer data from any register to any other register in the CPU

The following

path way is used to

execute

ALU instructions

(e.g.:

add r0, r1, r2 and

mov r0, r1):

This path fetches data from registers to the ALU and send the result to a register

The branch instruction is included because the PC (program counter) is one of the registers !!!

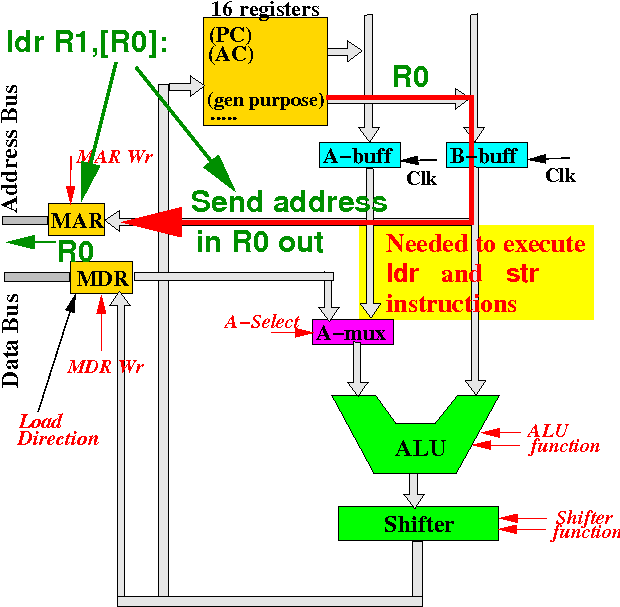

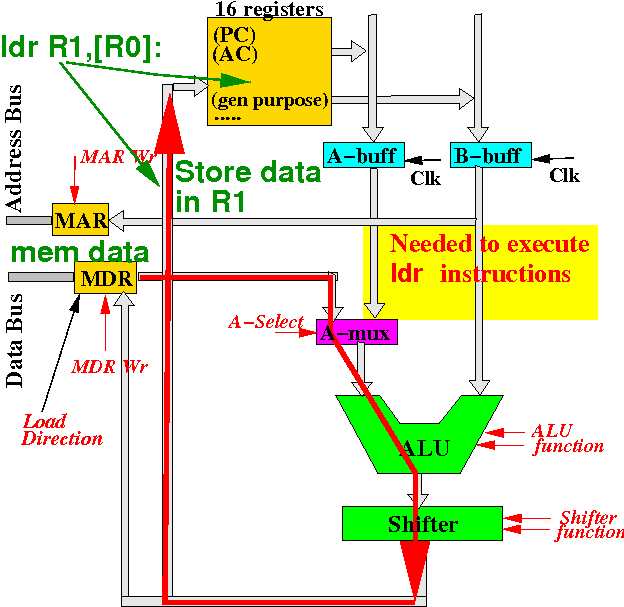

To execute a "load" instruction (e.g.: ldr r1,[r0]), the CPU must send the address in a register on the address bus to read the memory location:

Step 1: we need a path to transfer data from a register to the MAR

After the data from memory is fetched in the MDR register, we must forward the fetched data into a register:

Step 2: we will also need a pathway from the MDR register to registers

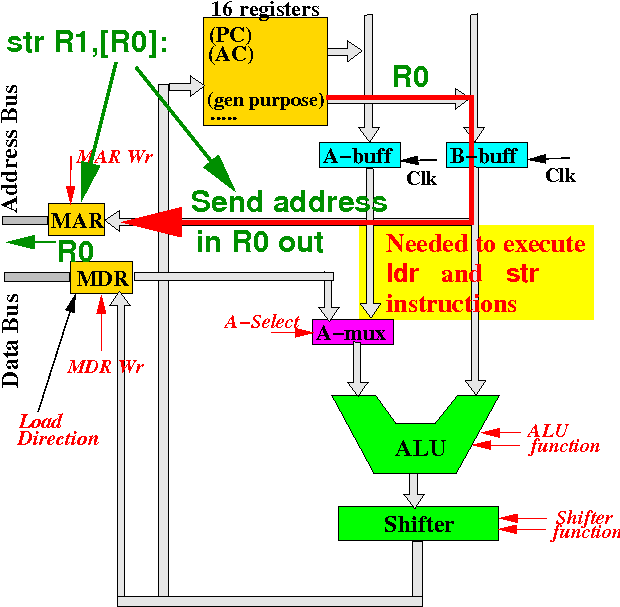

To execute a "store" instruction (e.g.: str r1,[r0]), the CPU must send the address in a register on the address bus to write it to memory:

Step 1: we need a path to transfer data from a register to the MAR register

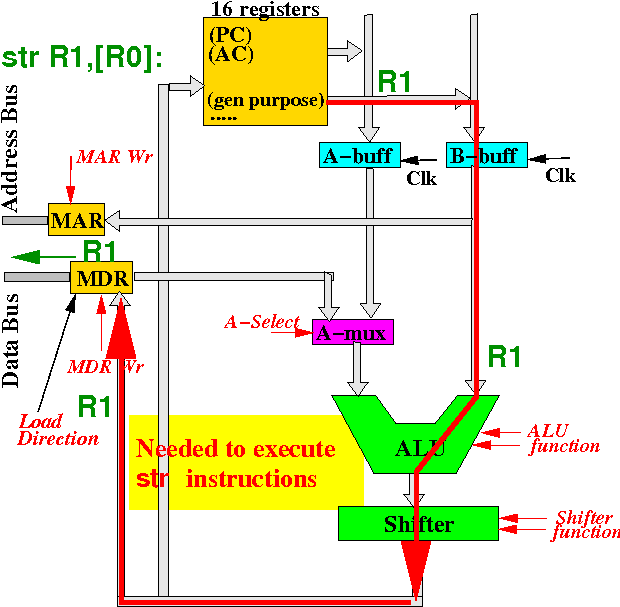

To execute a "store" instruction (e.g.: str r1,[r0]), the CPU must also send the data in a register on the data bus to read the memory location:

Step 2: we will also need a pathway from the registers to the MDR register

Review: the CPU repeatedly executes the following steps in the instruction execution cycle:

|

These steps must be executed in the above ordering !!

We will study how to sequence events using clock signals

|

|