|

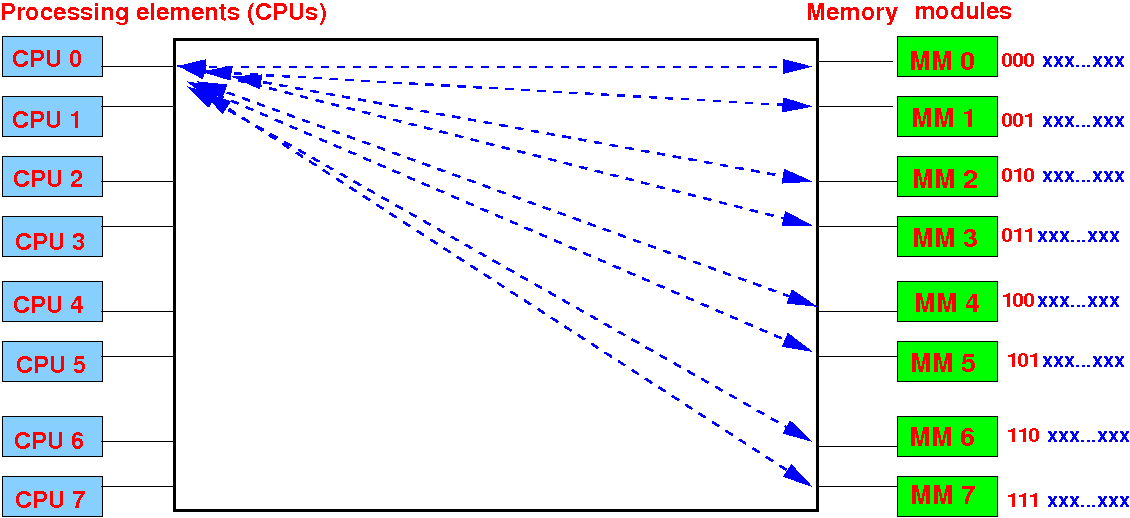

Property 1: the interconnection network must enable any CPU to access any memory bank

Property 2: when multiple CPUs want to access the same memory bank, only one will succeed:

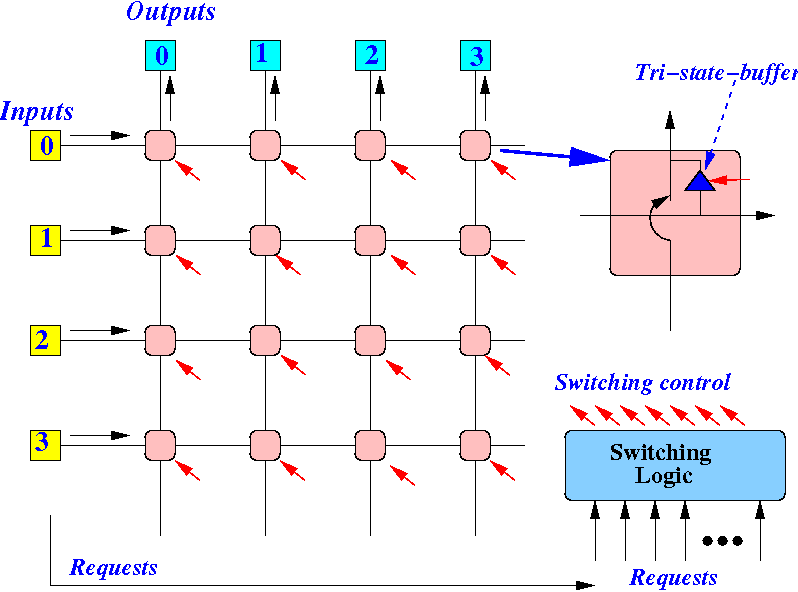

A cross bar interconnection network (or switch) connect its inputs to it outputs in a matrix manner:

A connect from an input to an output can be made by activating the correct tri-state-buffer

The connection between an input and an output is made when the tri-state-buffer is activated:

A connect from an input to an output can be made by activating the correct tri-state-buffer

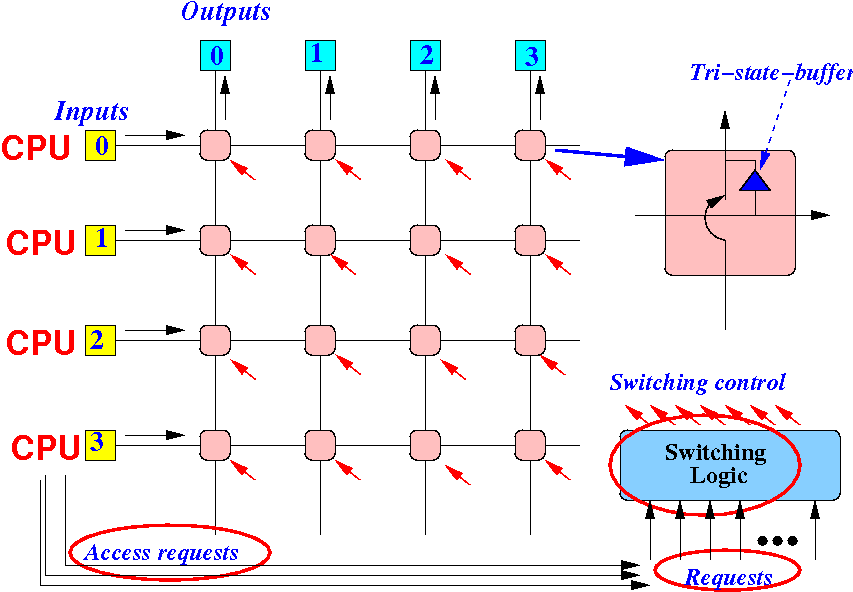

Each CPU sends a memory access request (that contains a memory address):

The switching logic circuit computes a setting of the tri-state-buffers to satisfy the CPU requests

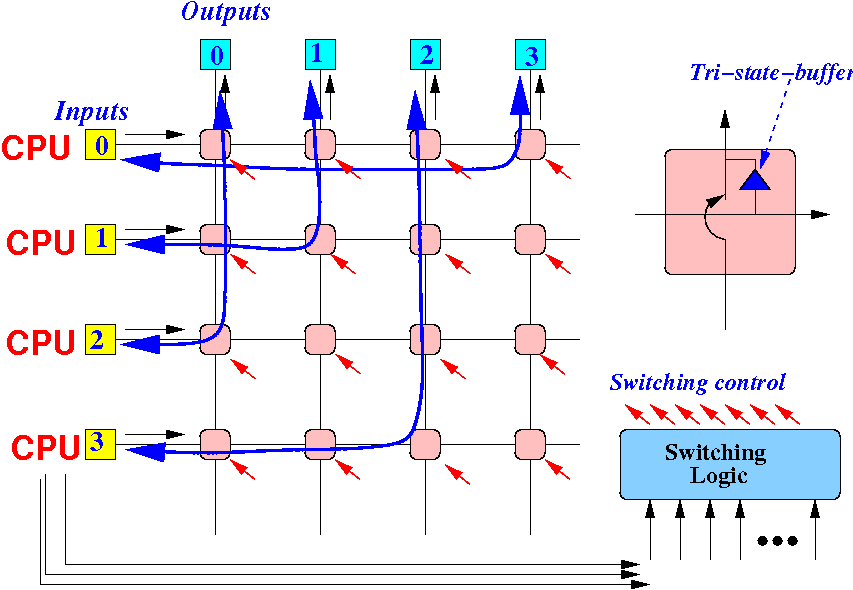

Example: CPU 0 wants to access memory bank 3, CPU 1 accesses memory bank 1, CPU 2 accesses memory bank 0, and CPU 3 accesses memory bank 2:

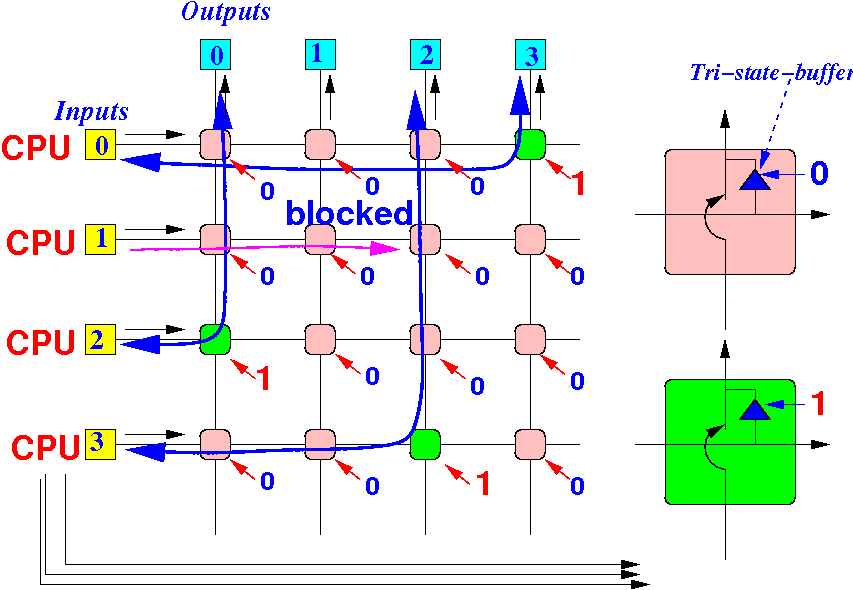

The switching logic circuit computes a setting of the tri-state-buffers to satisfy the CPU requests

Setting for: CPU 0 wants to access memory bank 3, CPU 1 accesses memory bank 1, CPU 2 accesses memory bank 0, and CPU 3 accesses memory bank 2:

The switching logic circuit computes a setting of the tri-state-buffers to satisfy the CPU requests

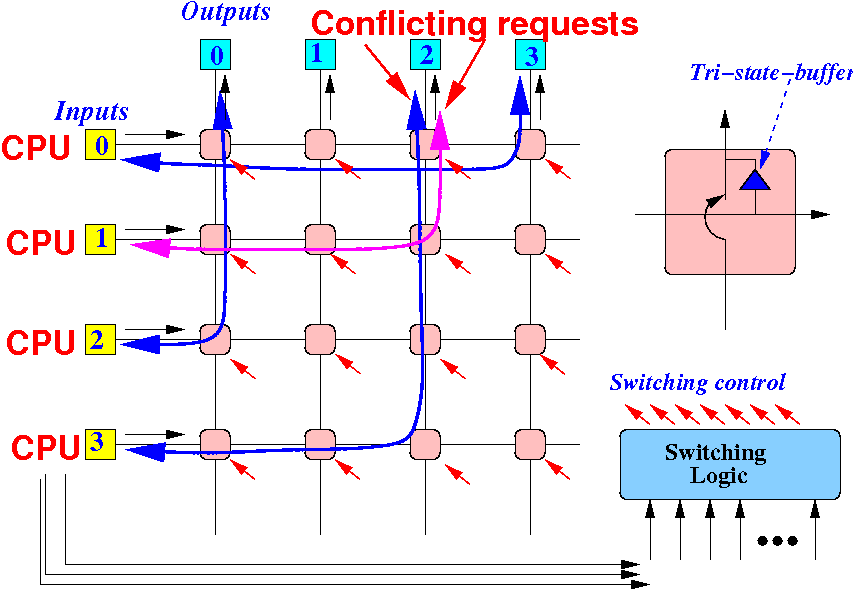

Example: CPU 0 wants to access memory bank 3, CPU 1 accesses memory bank 3, CPU 2 accesses memory bank 0, and CPU 3 accesses memory bank 2:

When multiple CPUs want to access the same memory bank, the requests are conflicting

Only ONE request among all the conflicting requests can be granted:

The unsuccessful CPU(s) will make the (same) request again in the next bus cycle

|

|