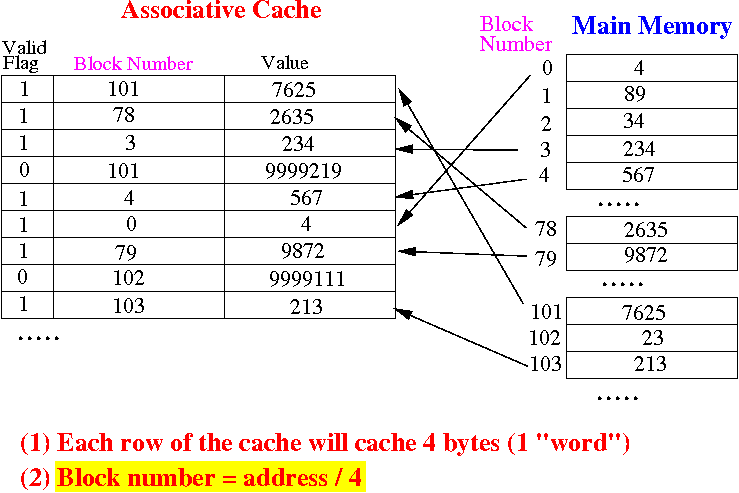

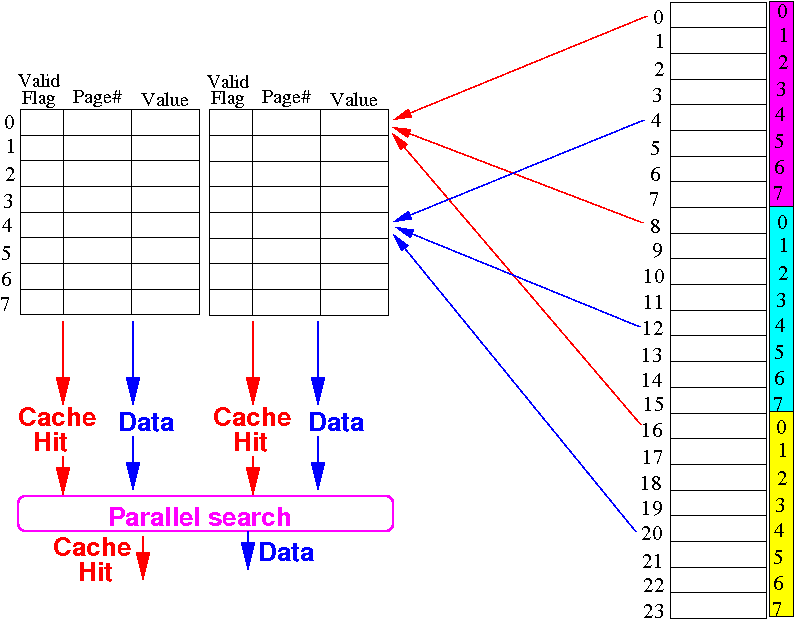

The associative cache can store data from any memory location in any cache slot:

BUT: it uses millions of compare circuits:

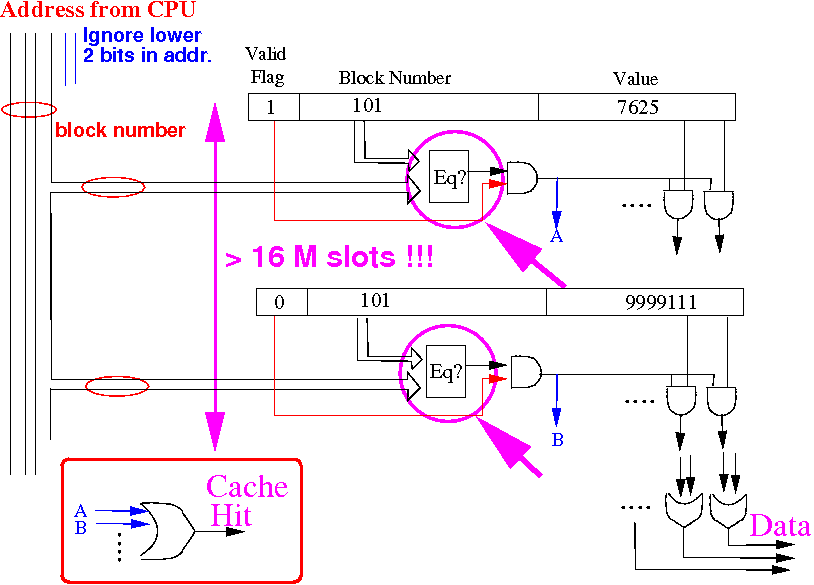

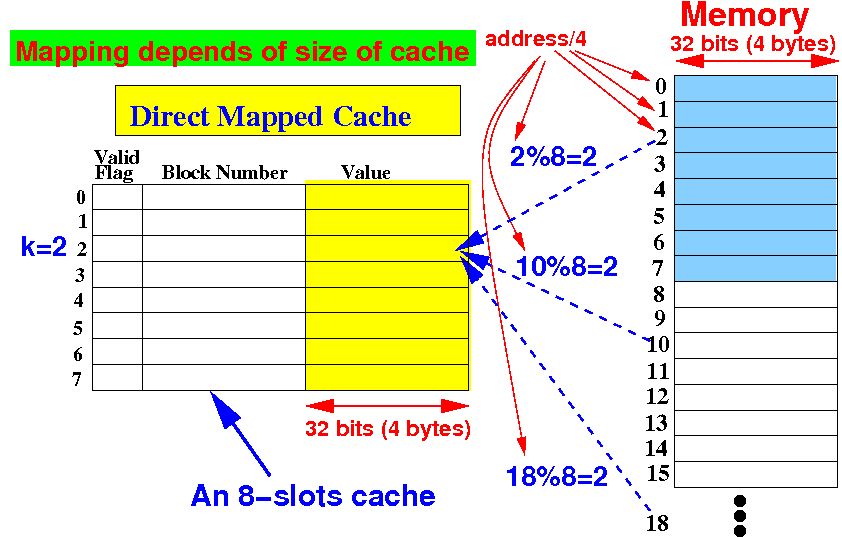

The direct mapped cache uses 1 compare circuit (and 3 sets of multiplexors):

BUT: data from a memory location must be stored in a specific cache slot:

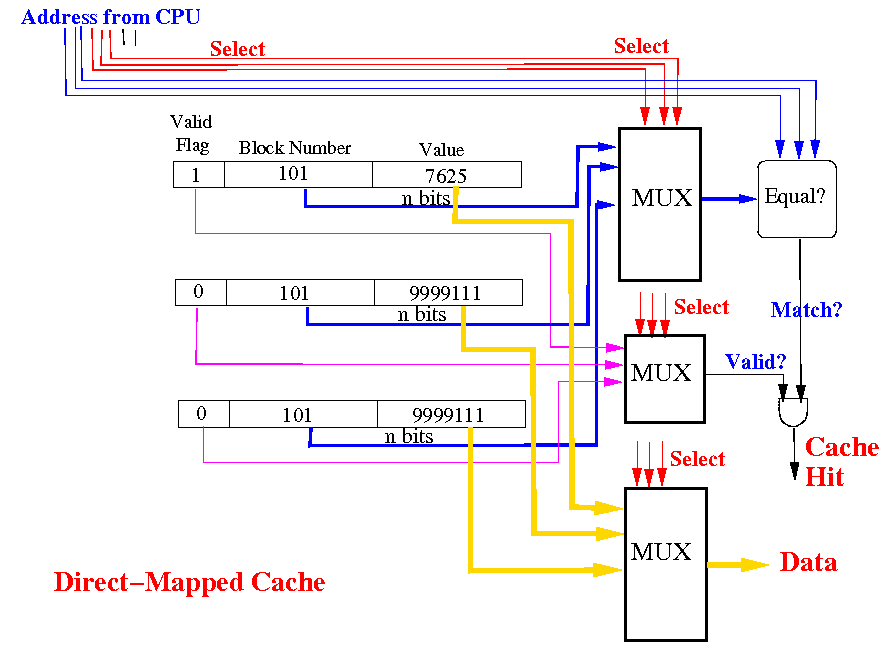

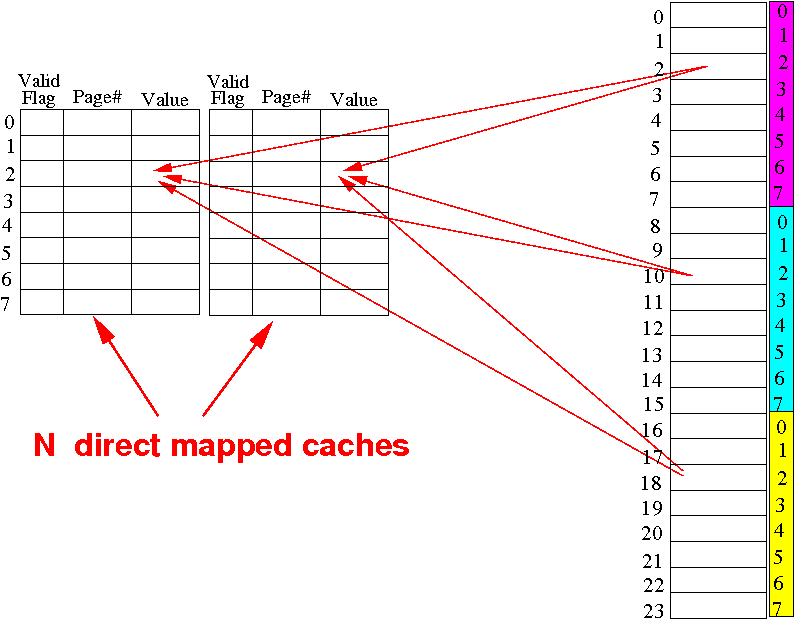

The set-associative cache consists of N direct mapped caches:

Data from memory can be stored in either direct mapped cache (but not in both caches)

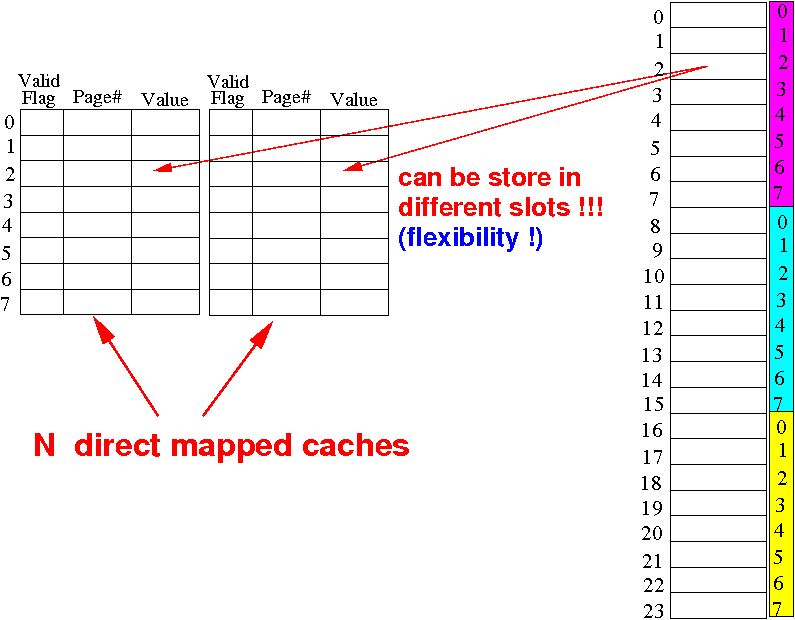

Data from a memory location can be stored in different slots in a set associative cache:

So we have achieve a higher level of flexibility !!

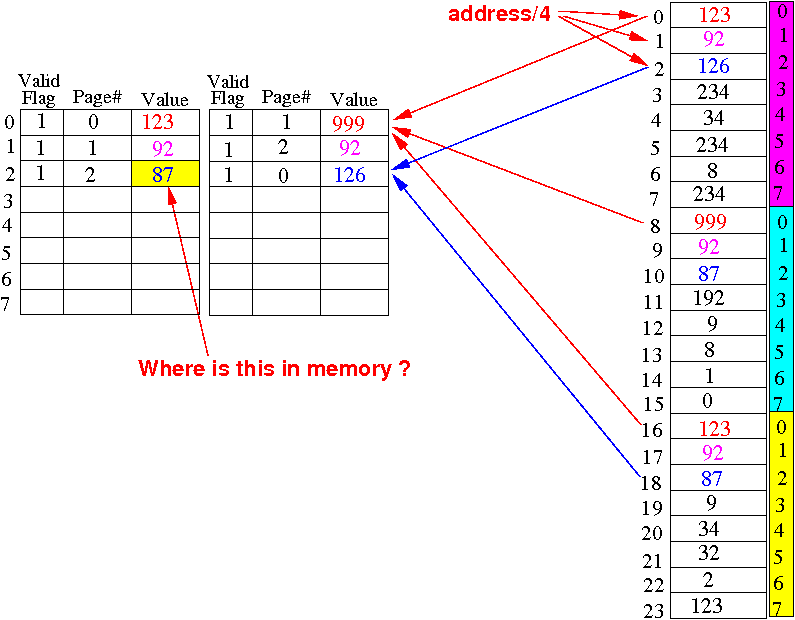

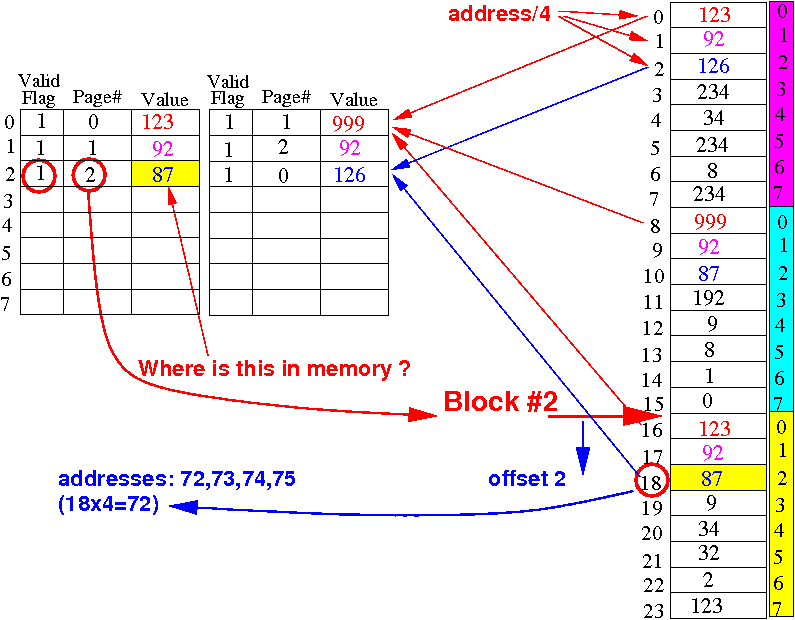

Consider the following content of a set associative cache:

Which memory addresses are cached in the highlighted cache slot ?

Answer:

The data is at offset 2 in block 2 in memory !

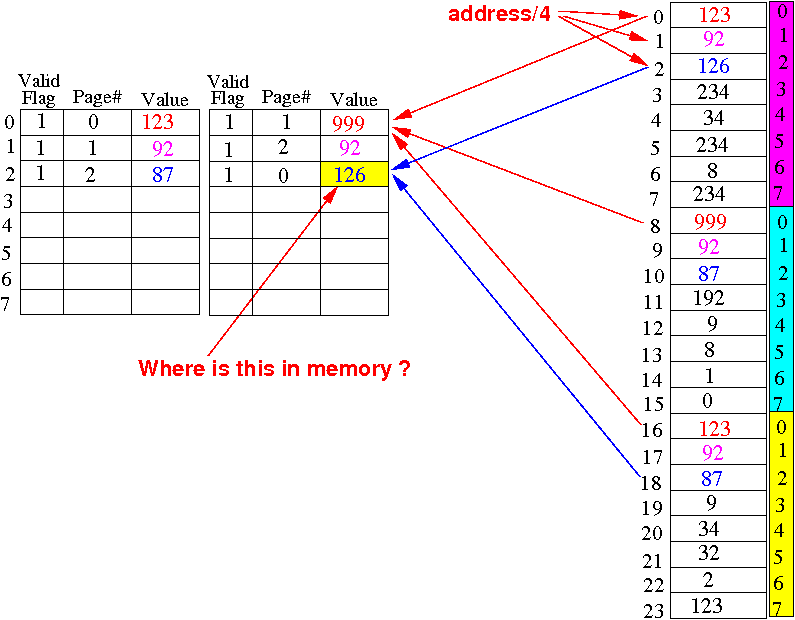

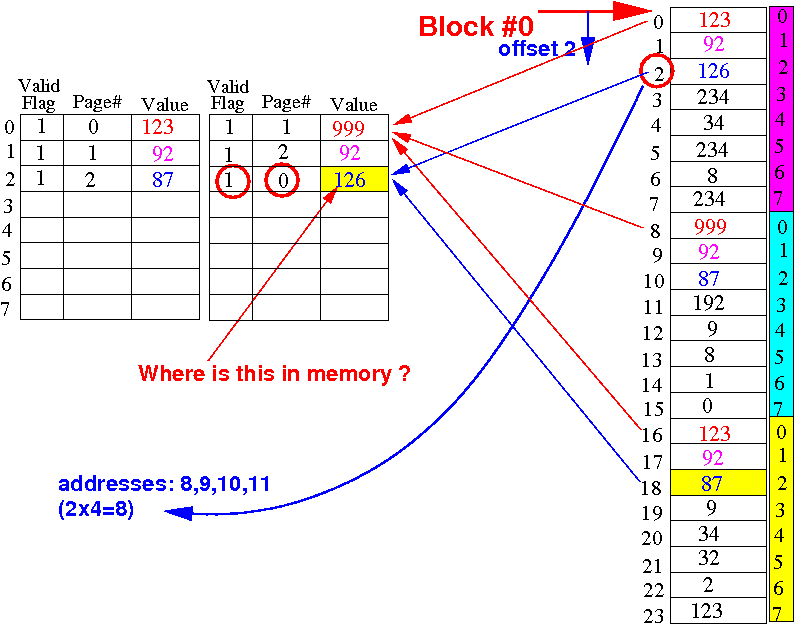

Consider the following content of a set associative cache:

Which memory addresses are cached in the highlighted cache slot ?

Answer:

The data is at offset 2 in block 0 in memory !

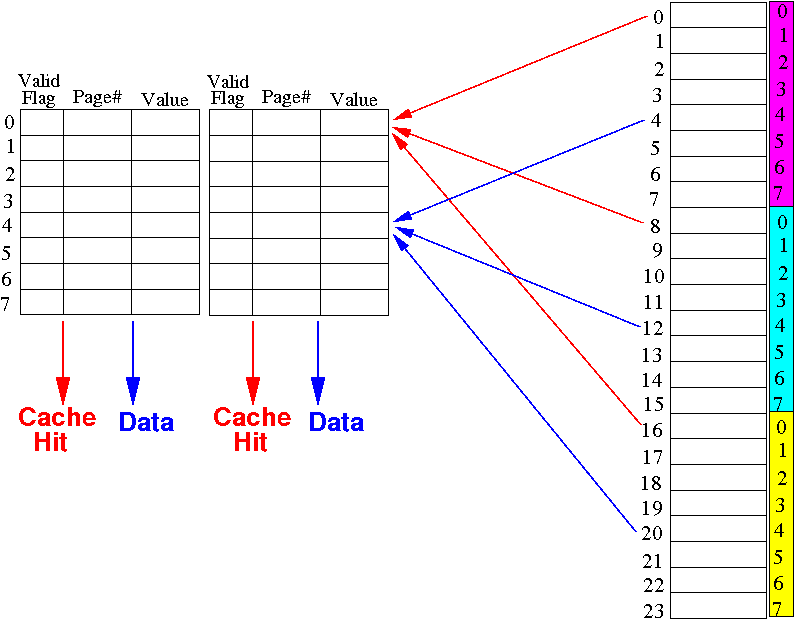

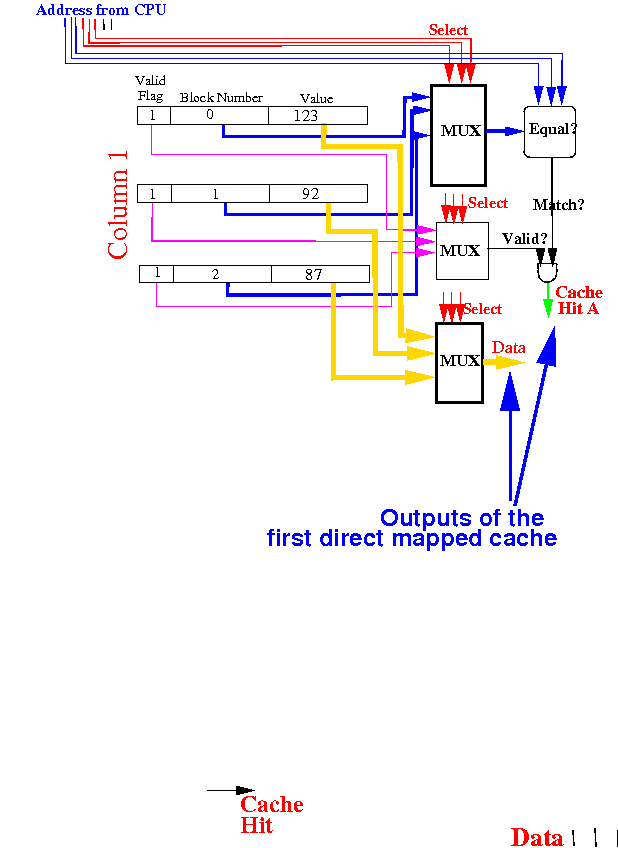

Recall: that each direct mapped caches will output a cache hit and data signals:

We need to combine the multiple outputs into a single result !!

We use the parallel search technique in the set-associative cache combine the results:

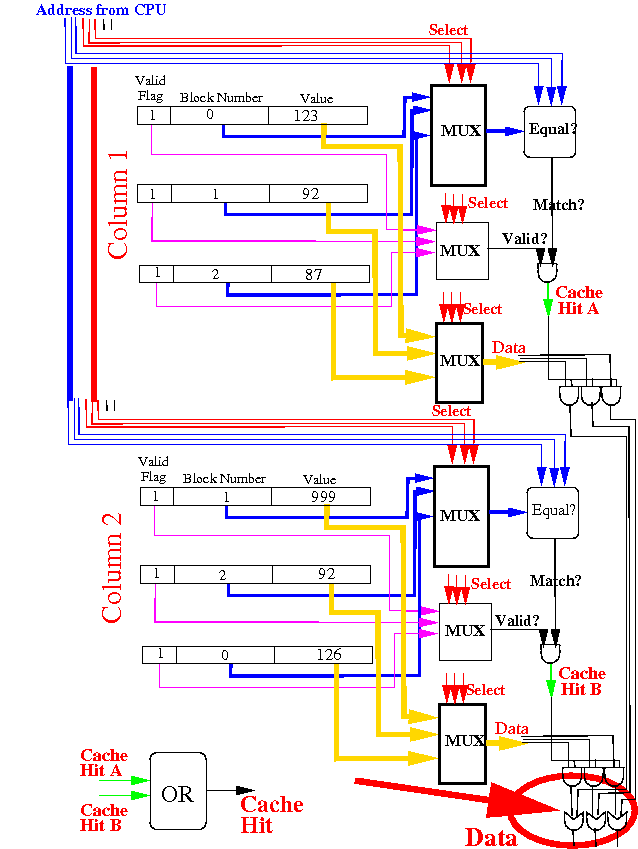

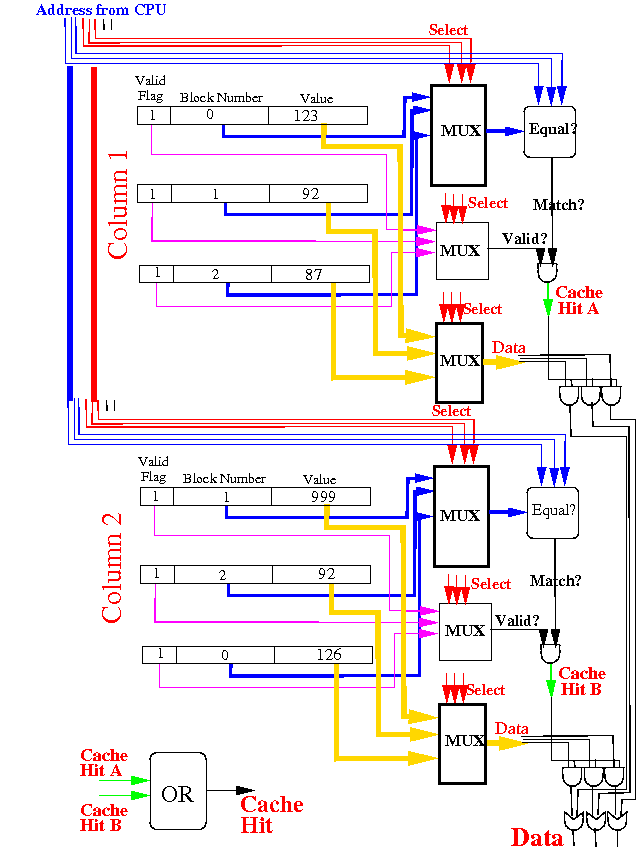

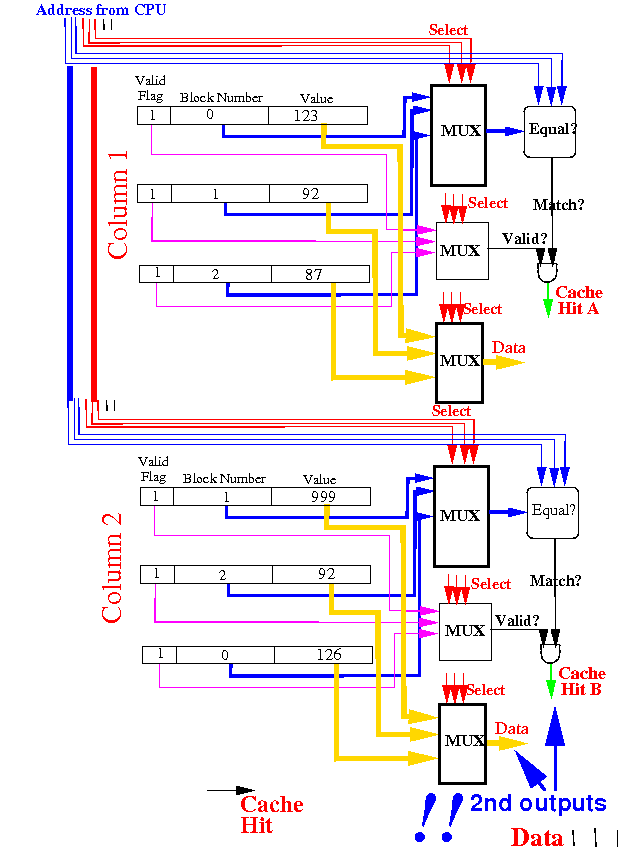

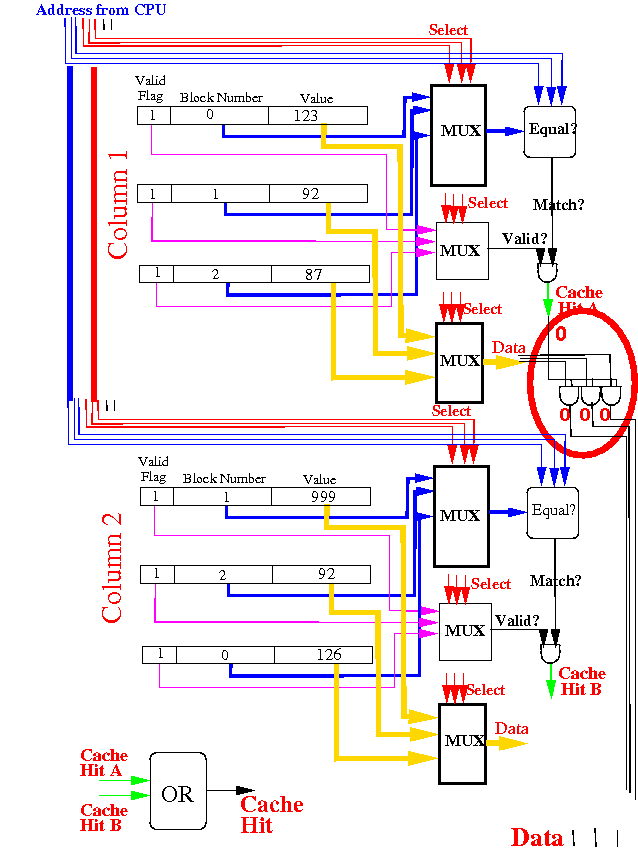

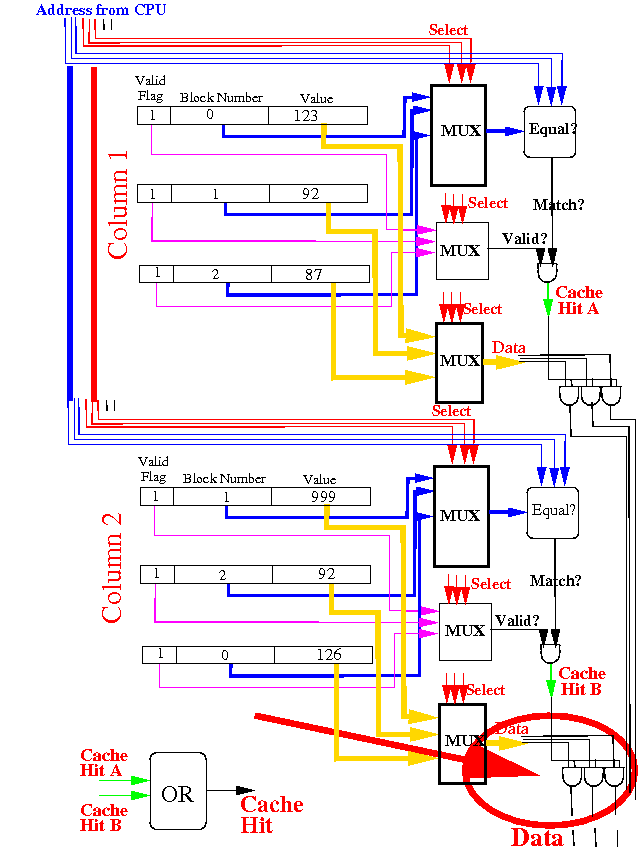

The following is the (simplified) circuit for a set associative cache:

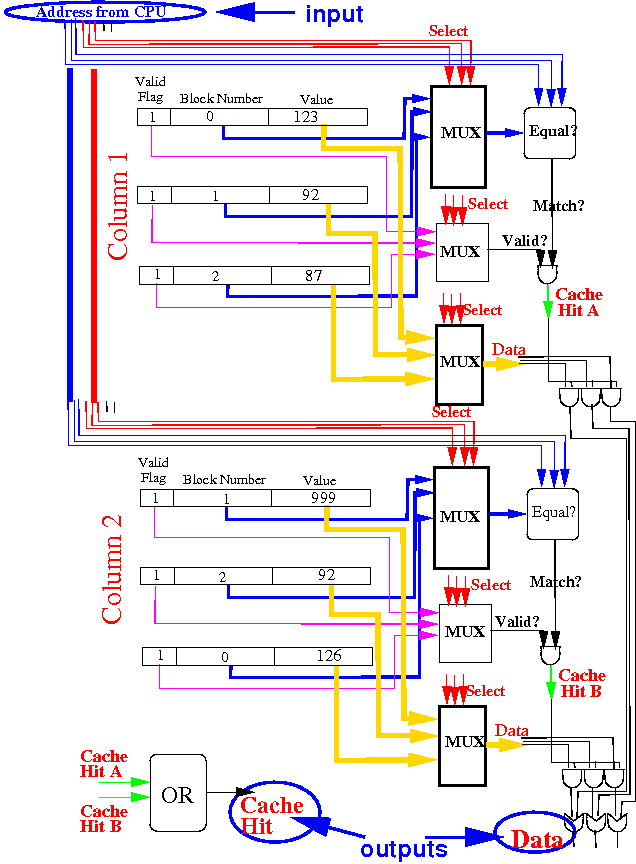

The input and outputs of the set associative cache are as follows:

We start with the input and output signals (I will only use 2 direct mapped caches)

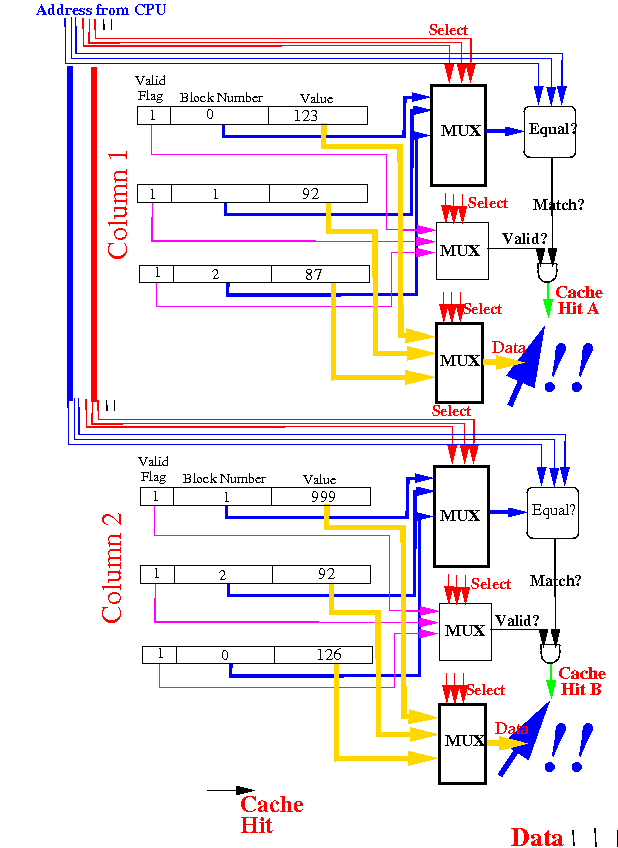

The first direct mapped cache will output its cache hit and data signals:

The second direct mapped cache will also output its cache hit and data signals:

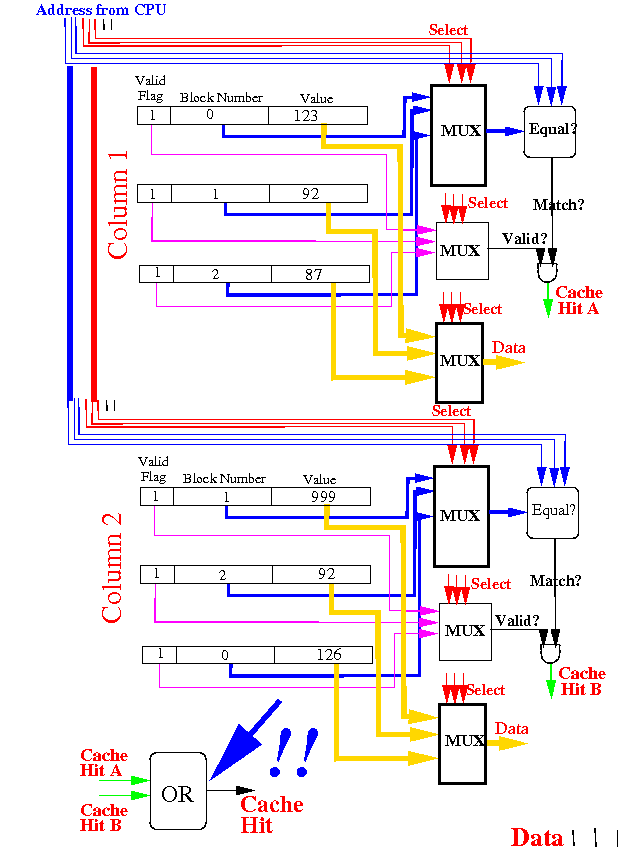

We have 2 "chances" to get a cache hit:

If (any) one of the direct mapped cache reports cache hit, we have a cache hit:

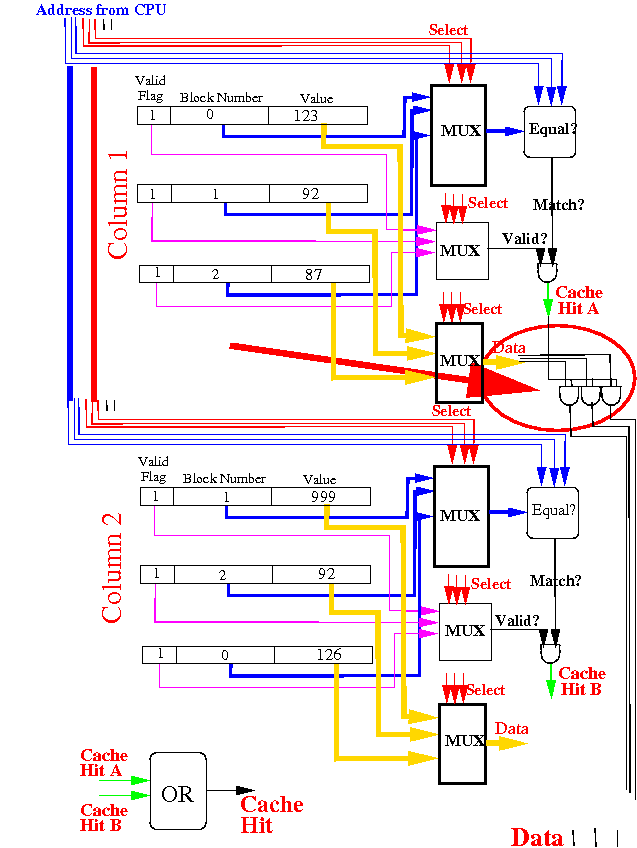

To obtain the data output, we first filter the cache 1's data by its cache hit signal:

When cache hit=0, the output are all equal to 0 and when cache hit=1, output=data:

We also filter the cache 2's data by its cache hit signal:

We use OR-gates to collect all the filtered outputs to form the data outputs: