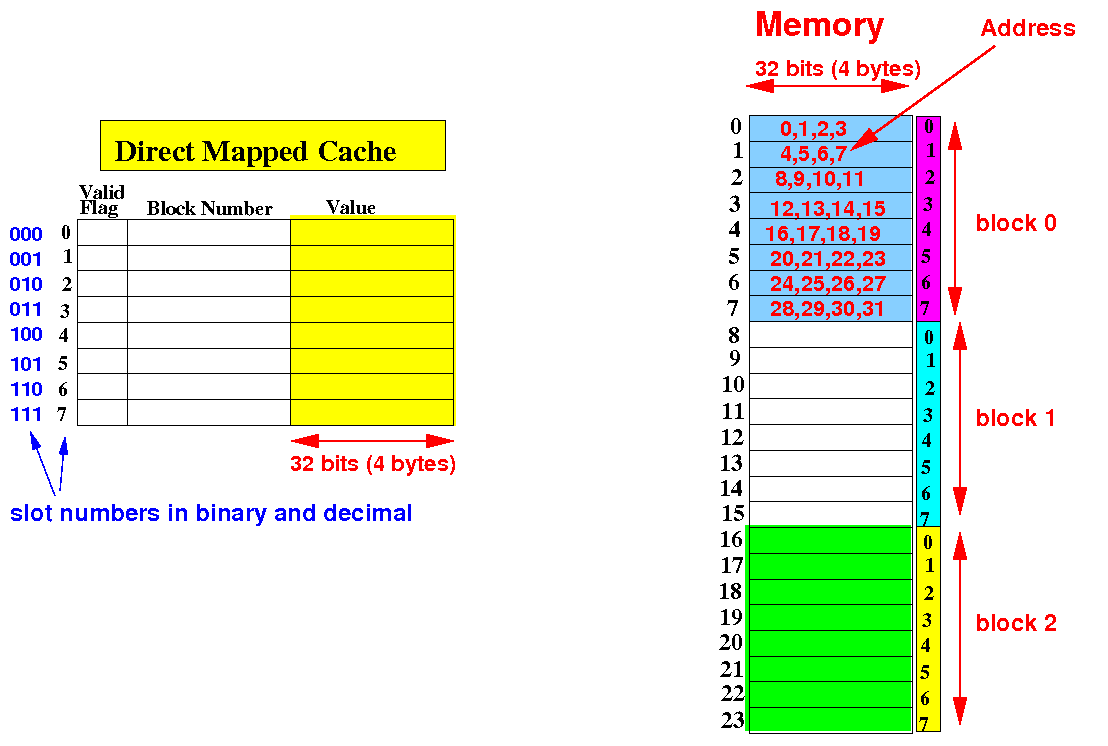

In order to construct a direct mapped cache, we must understand the various mappings:

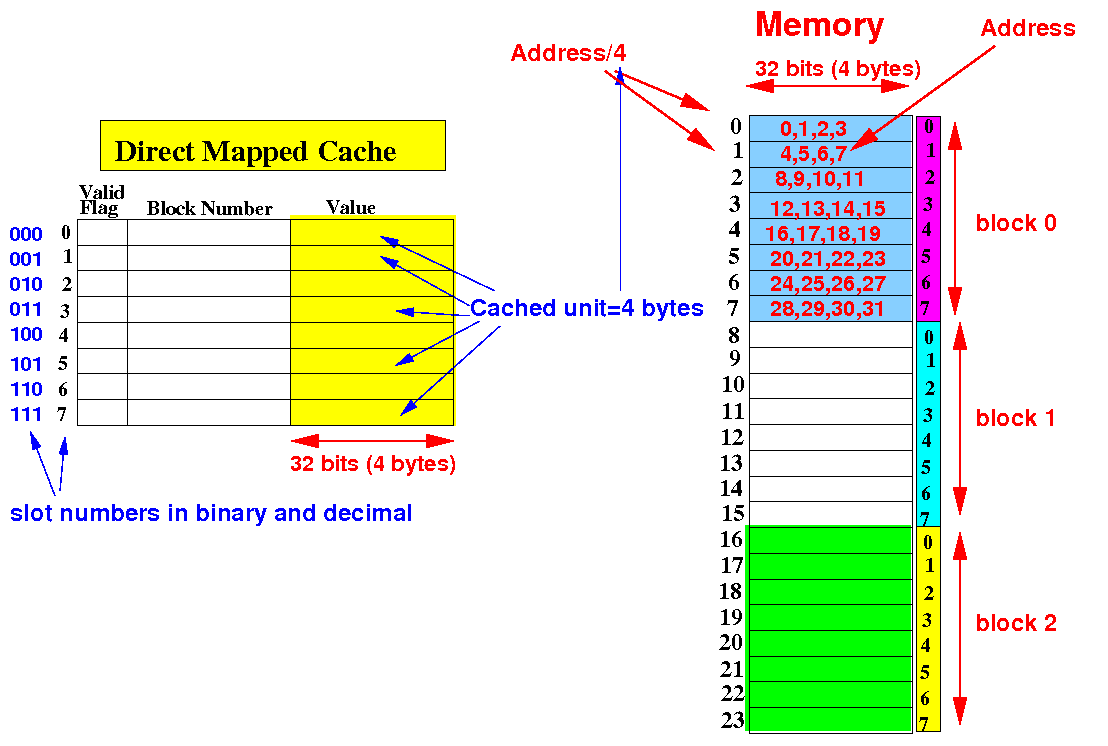

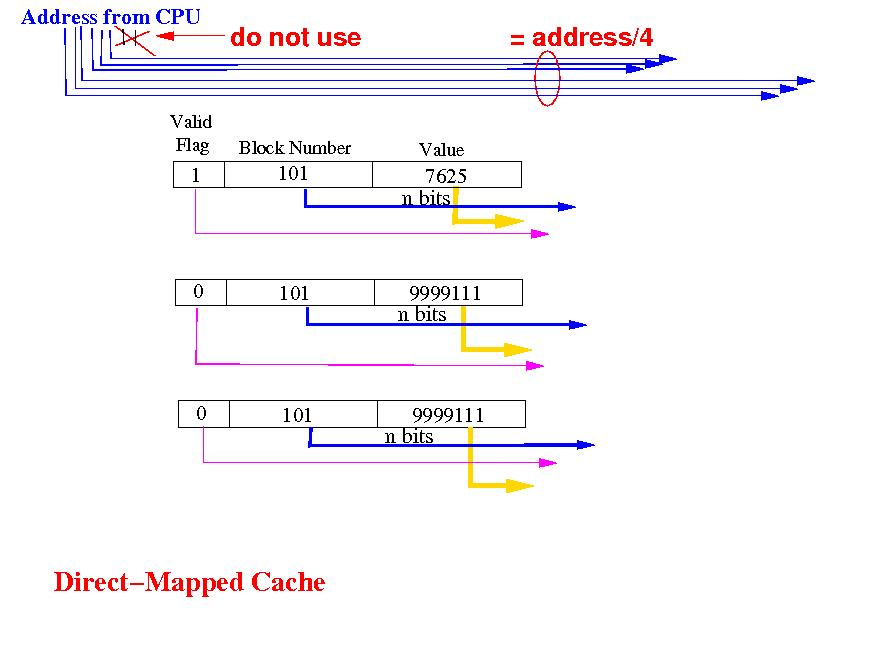

Because the cached unit = 4 bytes, we identify a "cacheable" memory unit with (mem addr)/4:

Recall:

(mem addr)/4 =

remove the

last 2 bits from

a mem addr

E.g.:

addr = 0000..00001100,

addr/4 = 0000..000011

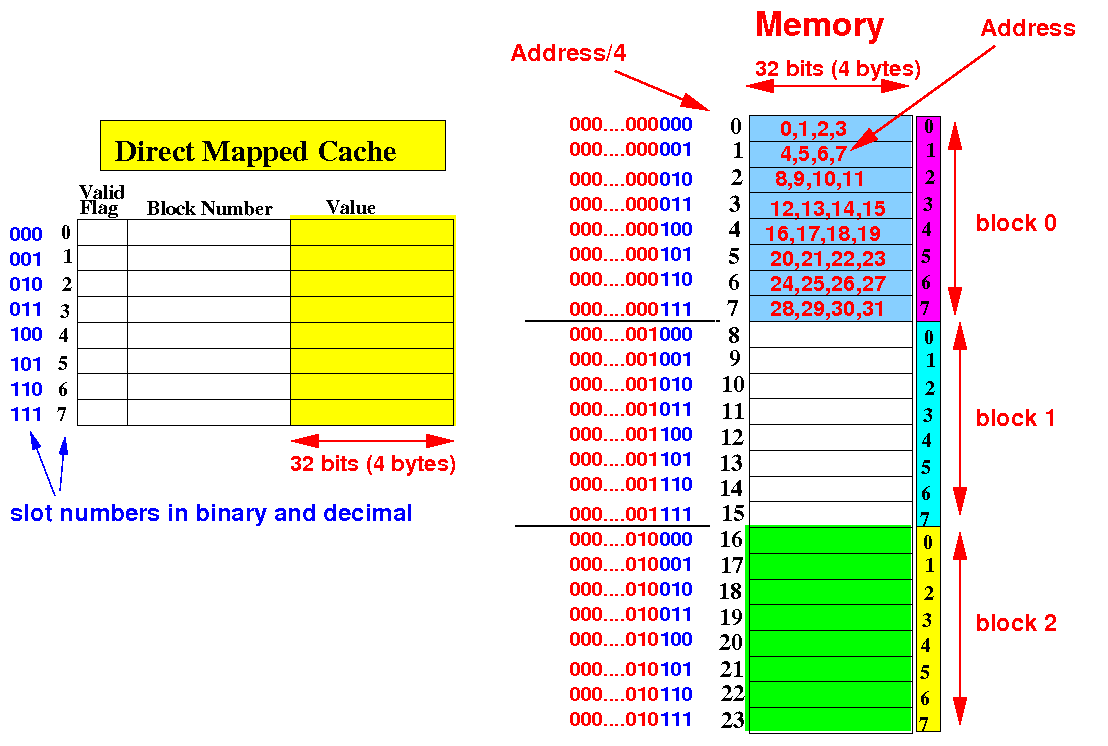

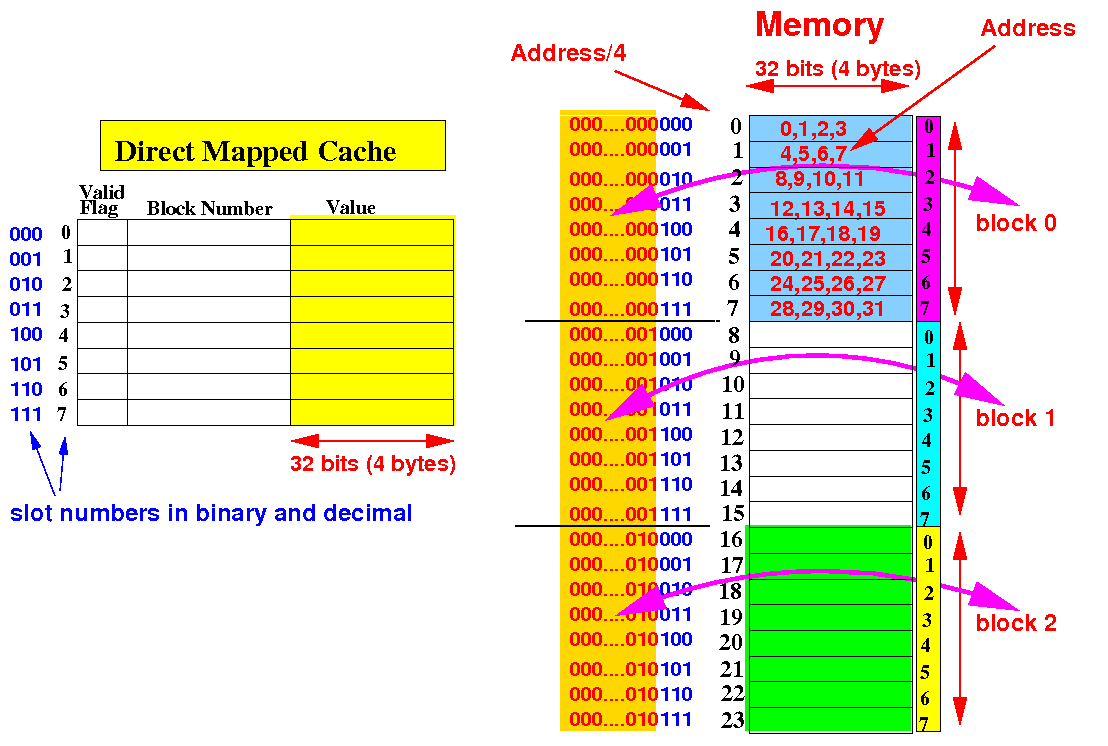

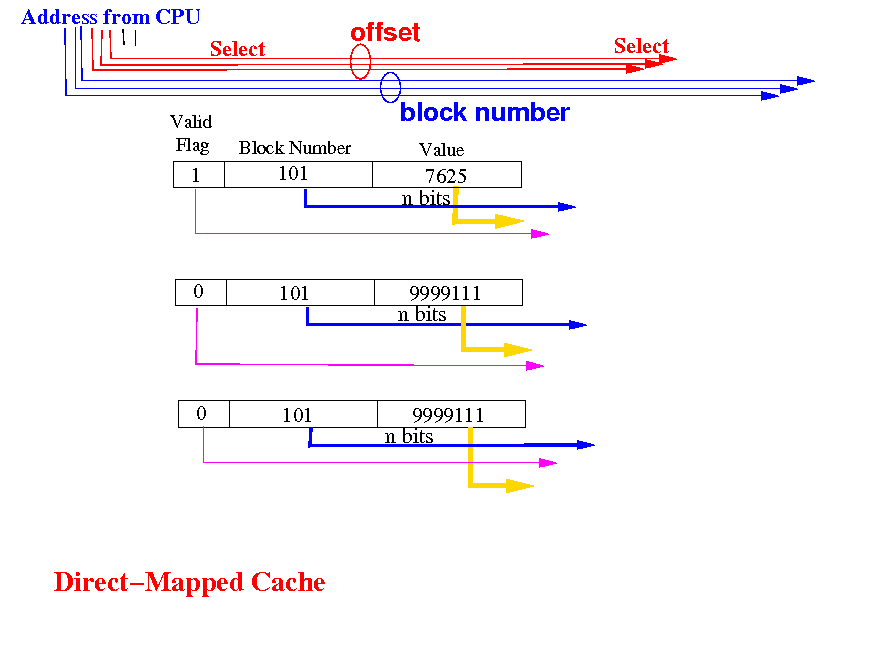

The mappings are easier to see when address/4 is expressed in binary:

Recall that the mapping depends on the cache size --- I used an 8 slots cache as example only !!

The block number is equal to (address/4) / cacheSize:

In the 8 slots cache, we divide by 8 and this is the same as removing 3 bits from (address/4)

The slot number is equal to (address/4) % cacheSize:

E.g.: the slot 2 (= 010) can cache data from addresses 8,9,10,11, 40,41,42,43, etc

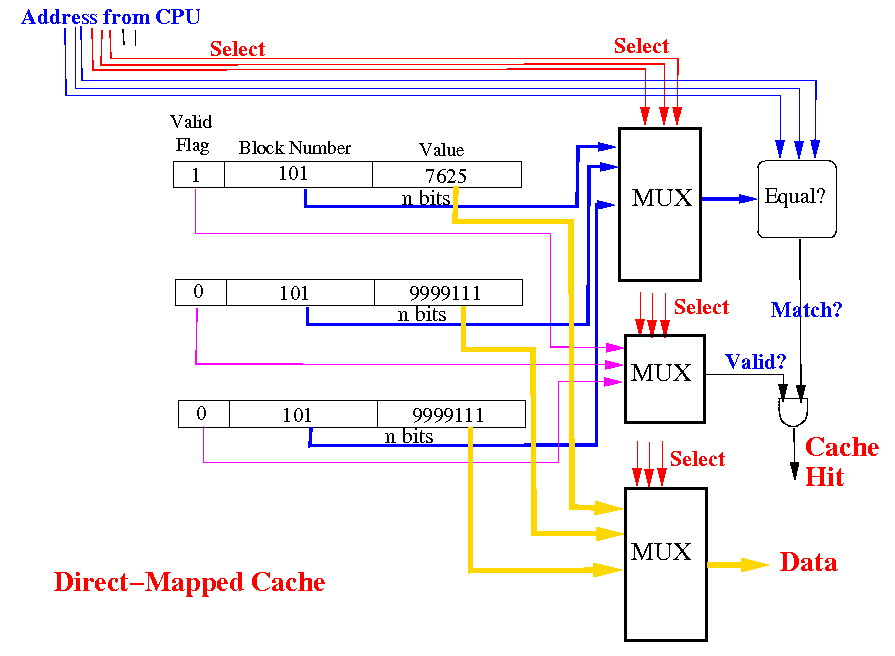

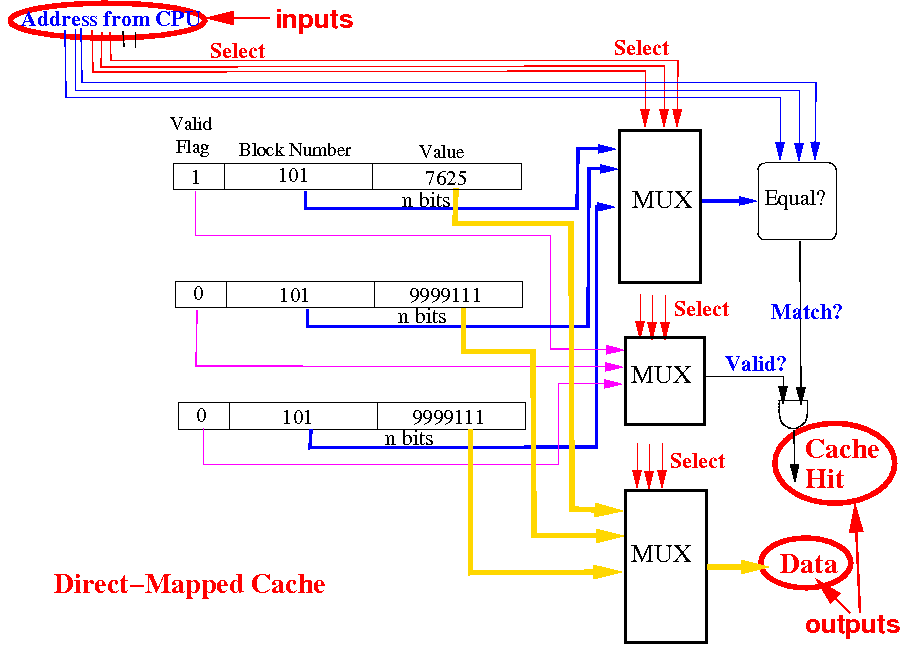

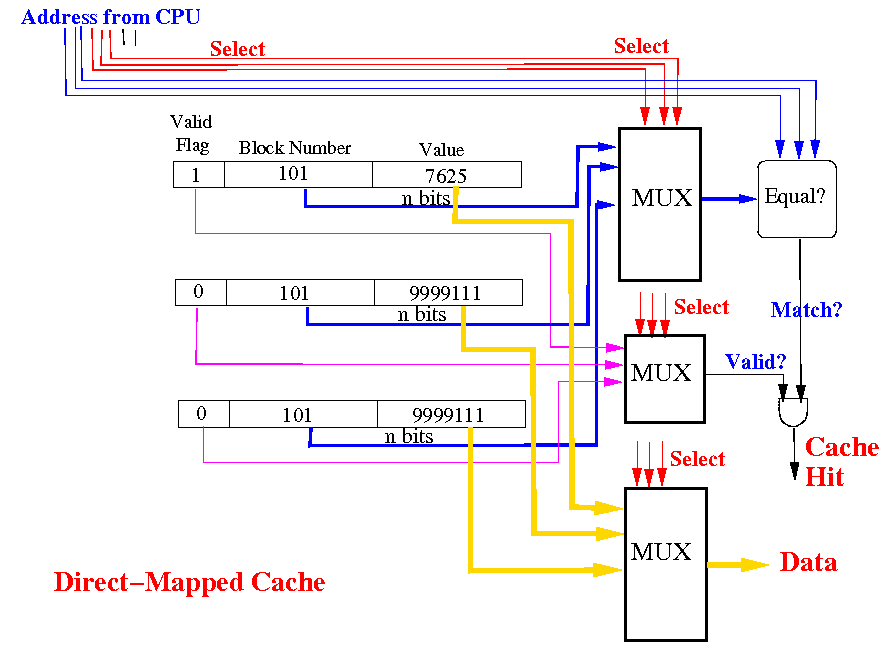

The direct-mapped cache can be constructed as follows:

I will explain the design in a piecemeal fashion next....

The inputs and outputs of direct-mapped cache circuit are:

Inputs: address from CPU (read request); outputs: cache hit (0/1) and data if cache hit=1

We first "compute" address/4 by omitting the last 2 address signals:

Recalls that the value address/4 comprises of 2 parts: BlockNumOffset

In this figure, I have assign the offset and block number with a different color:

The offset will determine which cache slot contains the data !!

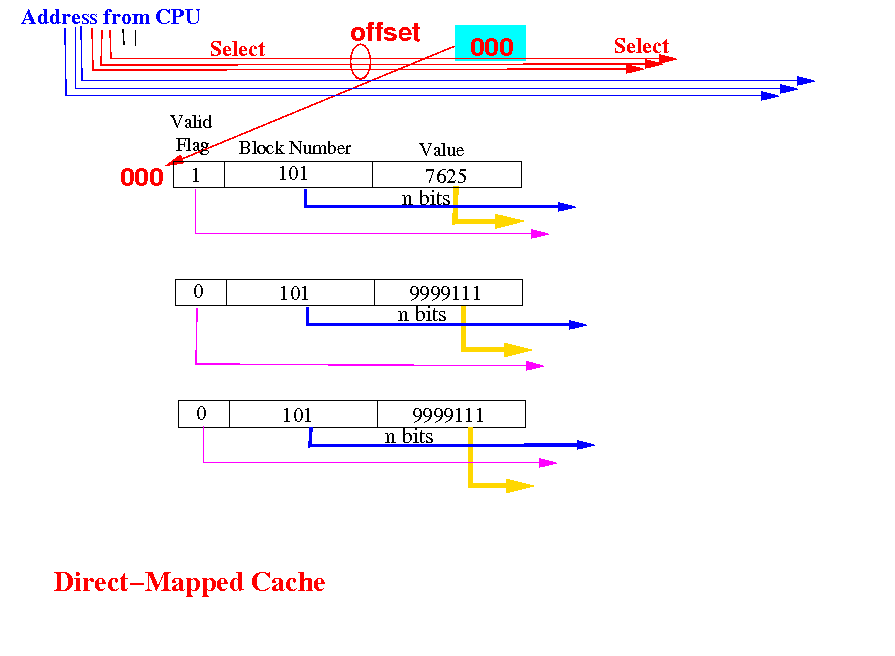

How the offset value determines the cache slot:

When offset = 000, the data will be stored in the slot 000

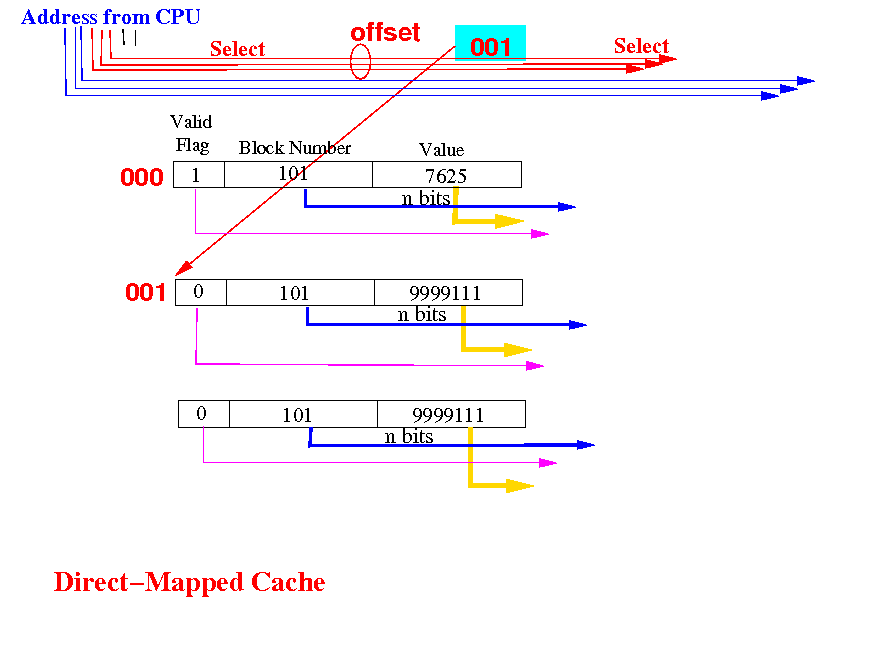

How the offset value determines the cache slot:

When offset = 001, the data will be stored in the slot 001 - and so on !!!

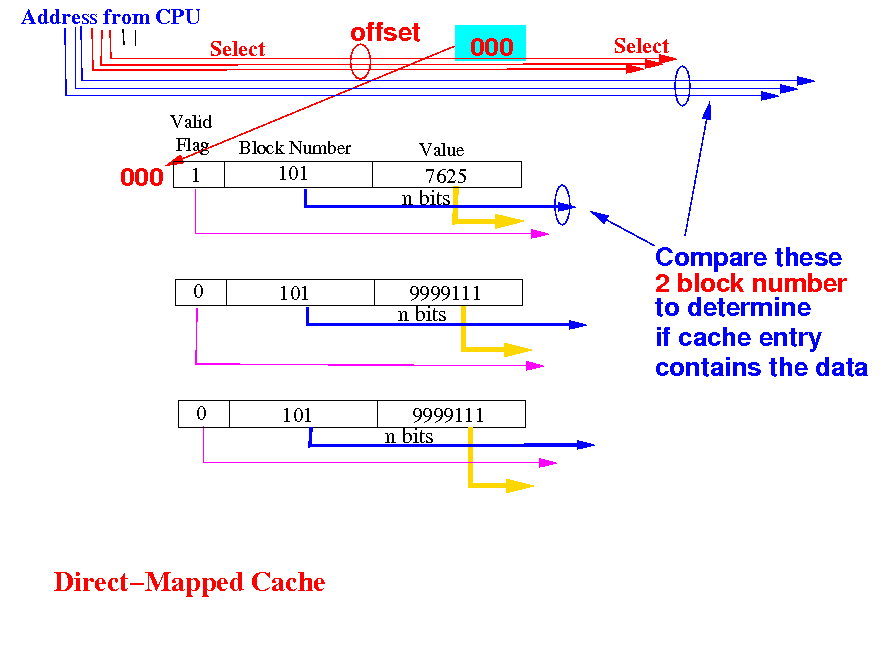

When offset=000, we must use the block number is slot 000 to determine cache hit:

If the 2 block numbers are equal, we have a cache hit (if valid =1)

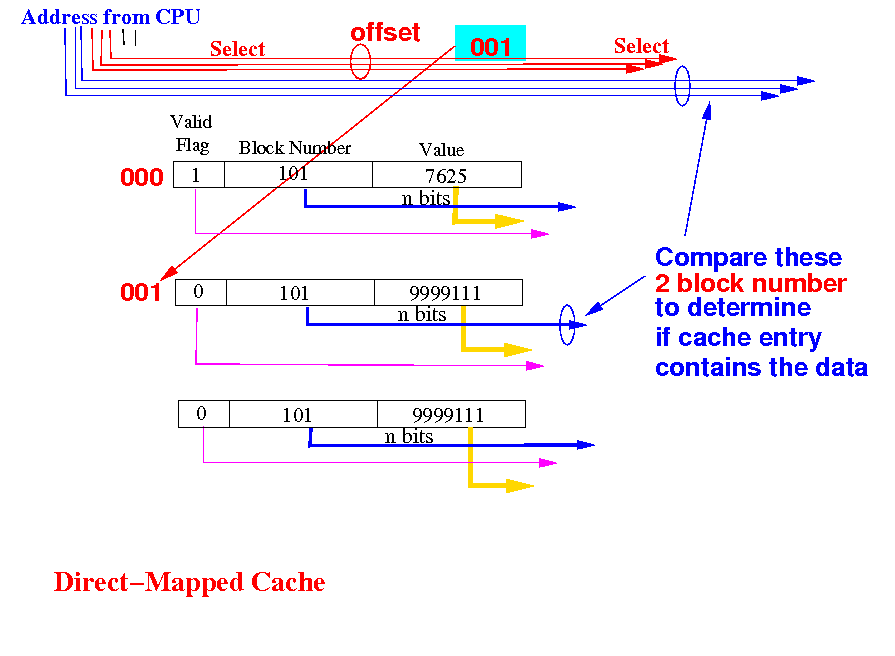

When offset=001, we must use the block number is slot 001 to determine cache hit:

If the 2 block numbers are equal, we have a cache hit (if valid =1)

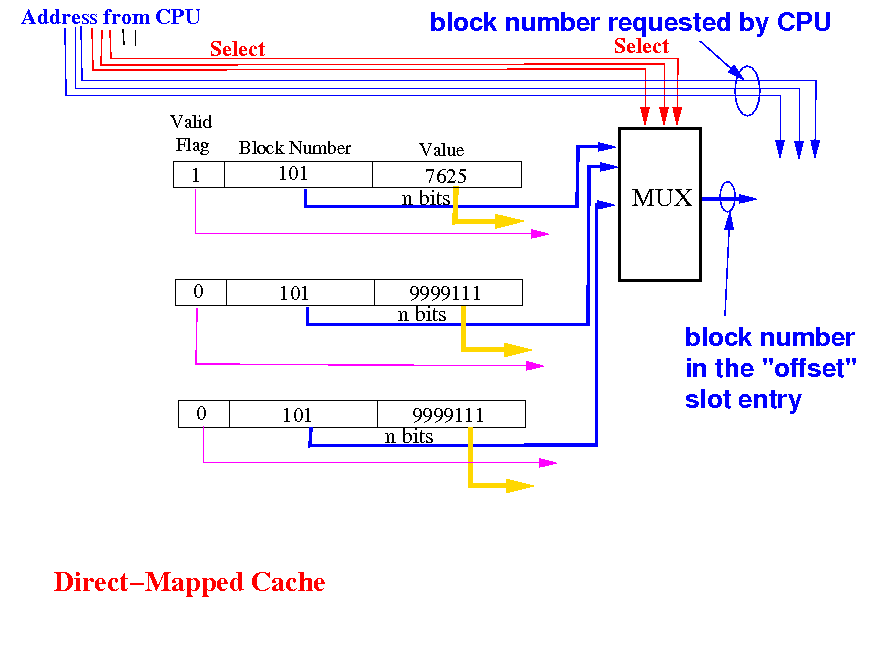

We can achieve this by using multiplexors to select the correct block number:

The output of the MUX is the block number in the "offset" slot in the cache

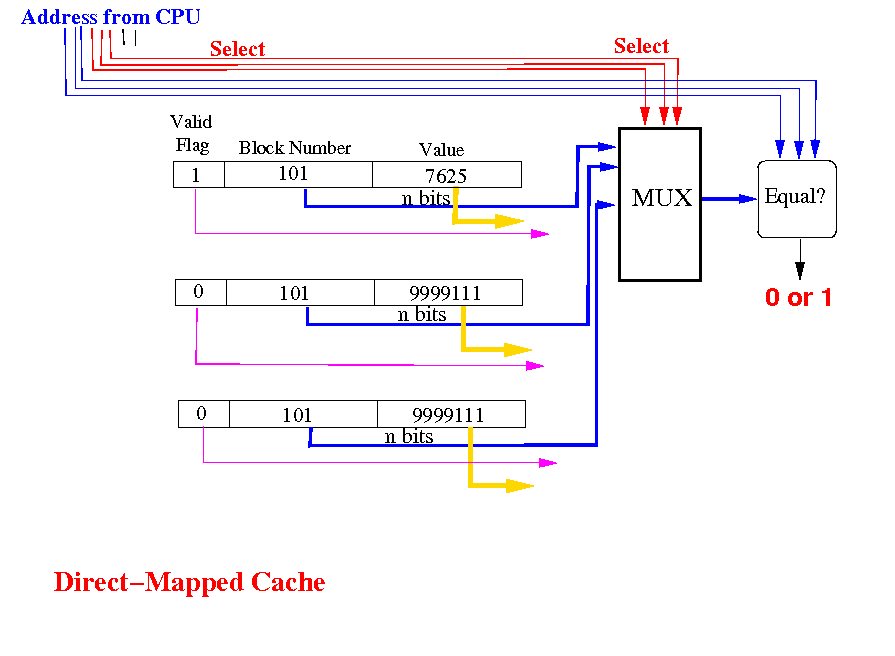

We check whether the 2 block numbers are equal:

To have a cache hit, the entry that store the data must be valid

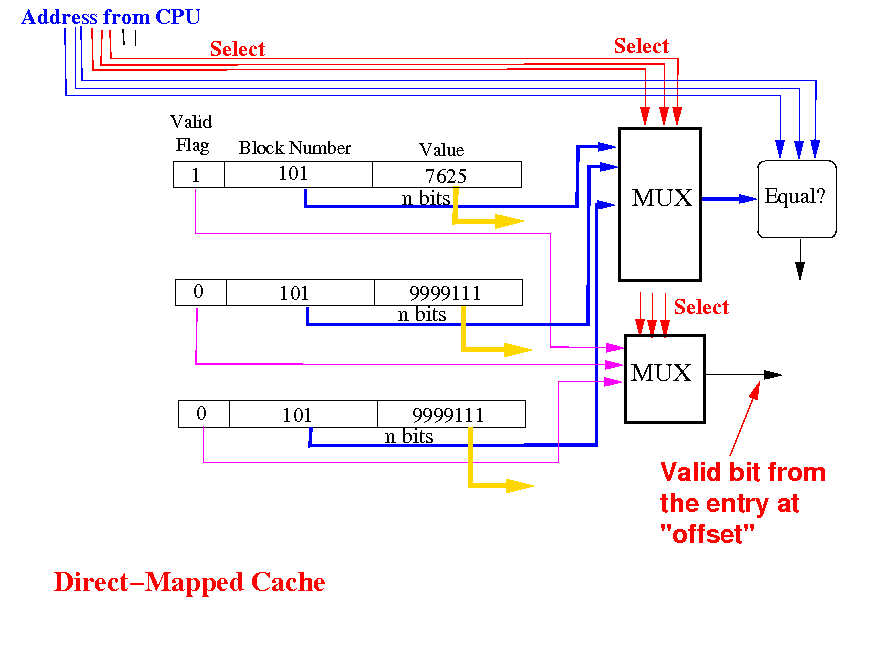

We first select the valid bit from the slot that stores the data:

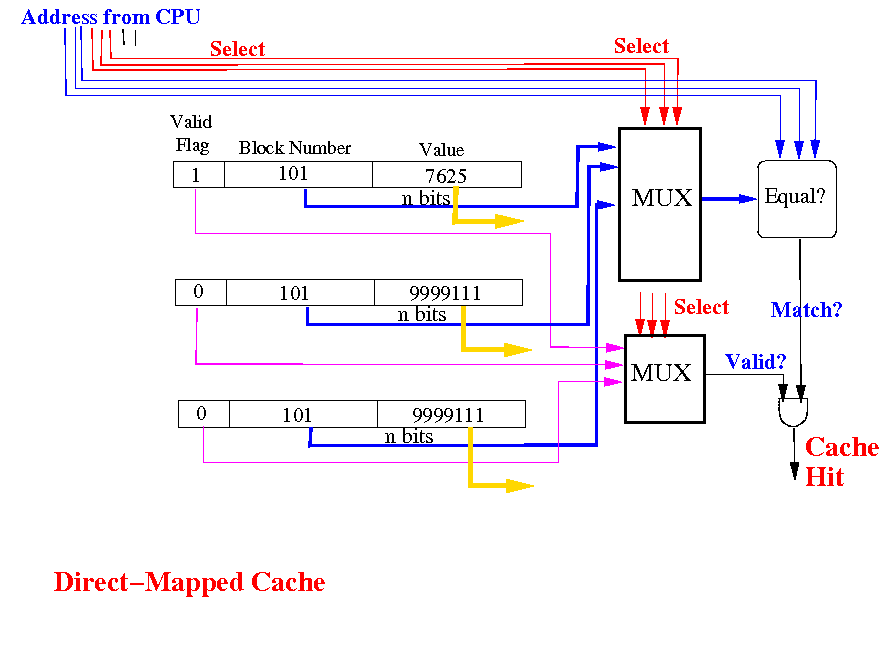

... and make sure that both condiions for cache hit are satisfied:

The Check Hit output = 1 when there is a cache hit and = 0 otherwise

The data stored in the "offset" slot entry is output as follows:

The cache will return the data output to the CPU only when: Cache Hit=1 !!

|

We will look at the set-associative cache next that combine the 2 caching techniques that we have studied