|

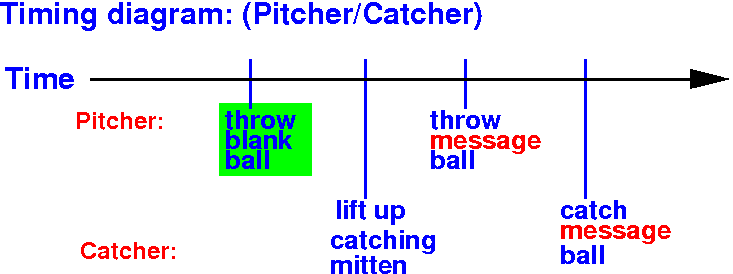

Problem description:

|

Give a set of rules to allow the pitcher to write a (braile) message on a ball and "send" (= throw) it to the catcher and the catcher will always "receive" (= catch the ball) it reliably.

Solution:

|

Notice: the progress of the steps in the protocol are "driven" by a readiness event

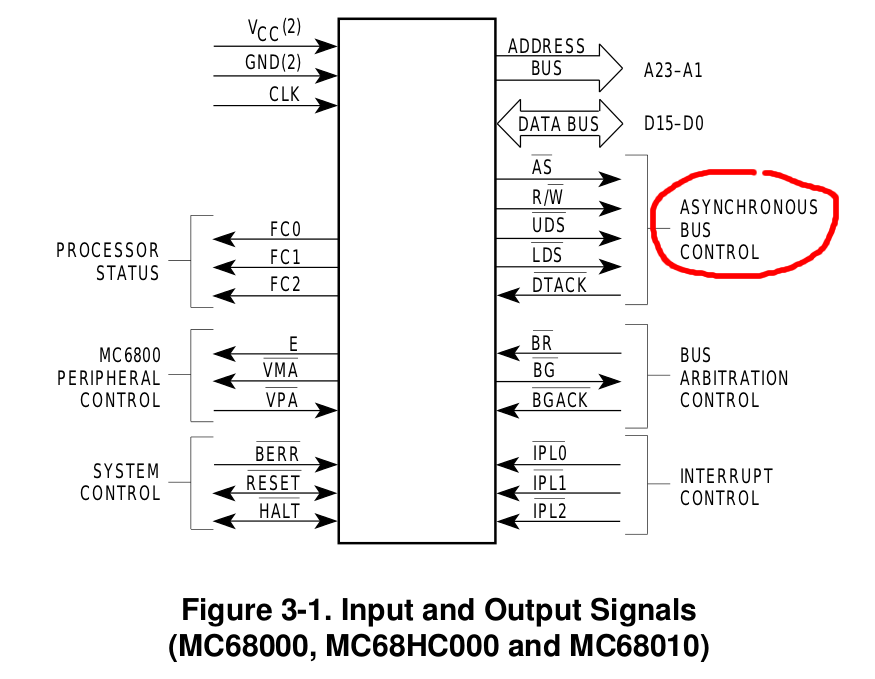

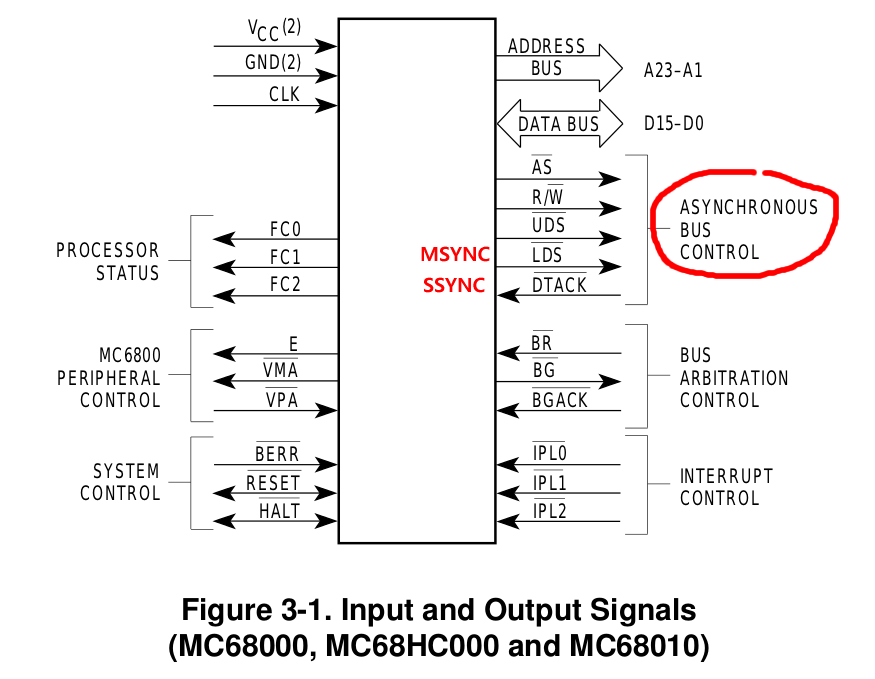

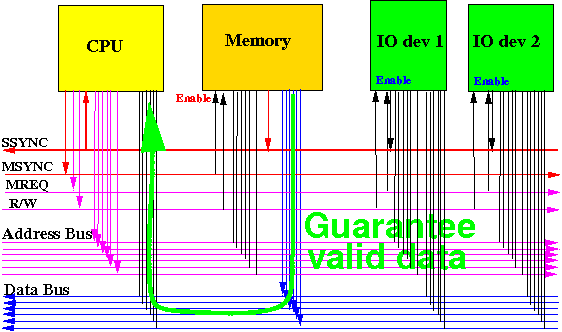

Signal names taken from a blue CPU (M68000):

Note: different CPU manufacturer can assigned different signal names to these signals !!!

Text books that presents a (simpler) asynchronous protocol uses these signal names:

We will first discuss the meaning of the new signals first.

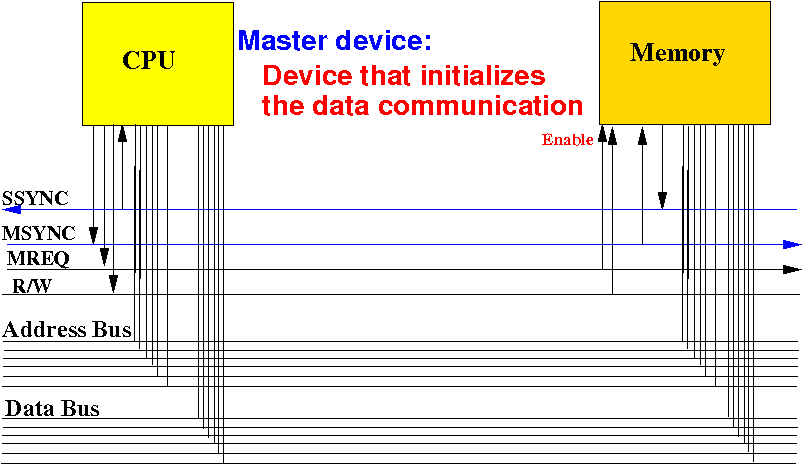

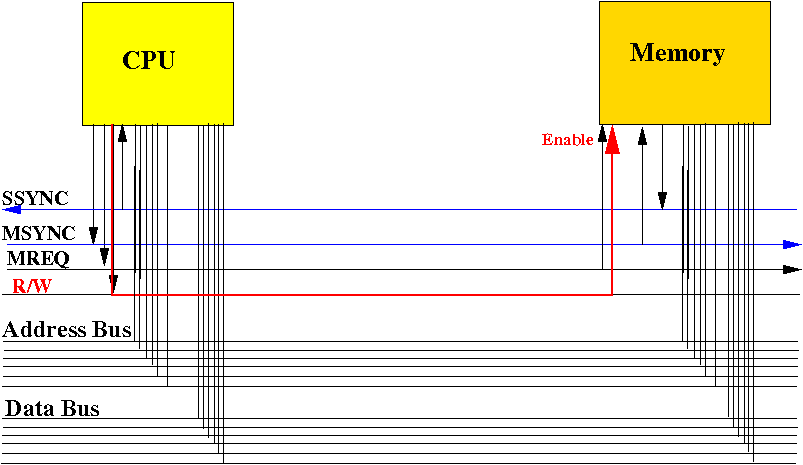

Master device = the device that initializes the communication procotol

In computer communication, the CPU is always the master device

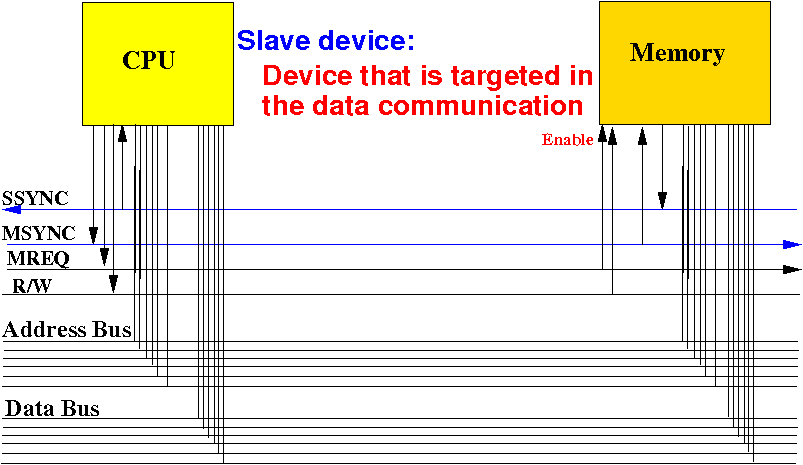

Slave device = the device that is targeted in the communication procotol

In computer communication, the memory is always the slave device

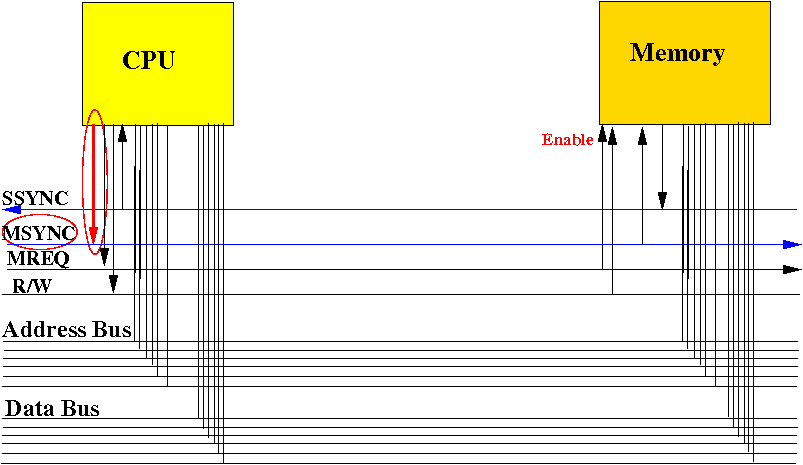

MSYNC is only asserted when the master device has sent out the Read/Write request

The MSYNC signal asserts that the command/request signals on the system bus is now correct

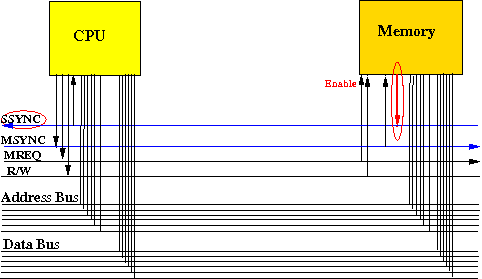

SSYNC is only asserted when the slave device has processed the Read/Write request

The SSYNC signal asserts that the response signals on the system bus is now correct

MREQ is only asserted when the memory is targeted (instead of an IO device):

The MREQ signal is used to activate (= enable) the memory circuit

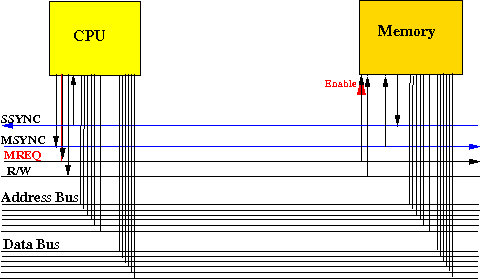

R/W is used to indicate a Read operation or a Write operation on the memory:

We will use R/W=0 to mean Read operation and R/W=1 to mean Write operation

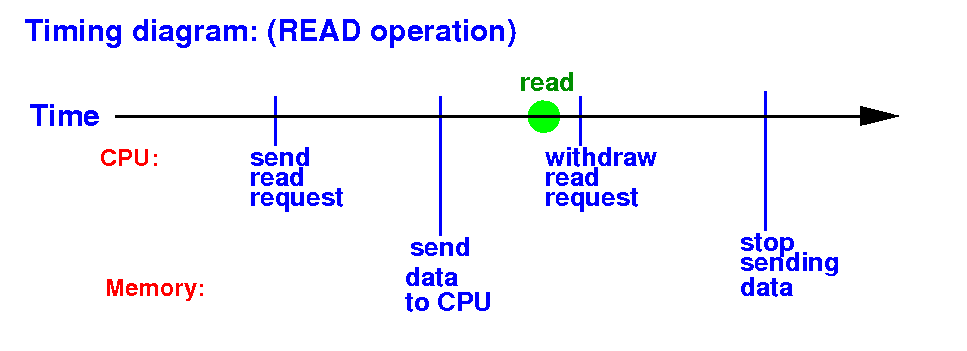

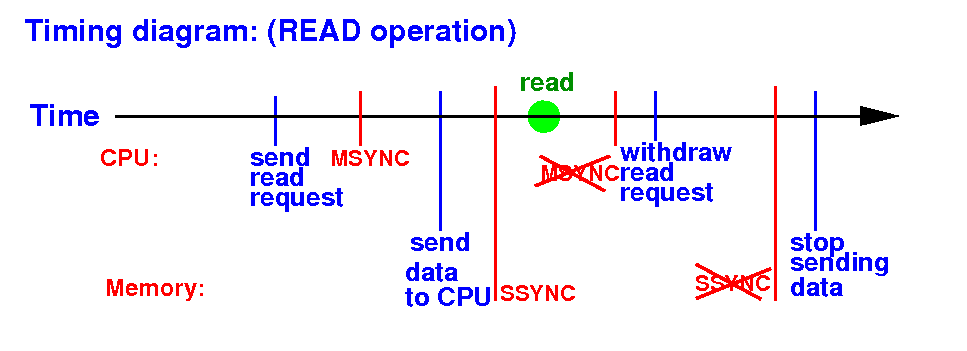

Protocol steps exchanged between the CPU and the memory in a READ operation:

The asynchronous protocol will add READINESS signalling to ensure correctness:

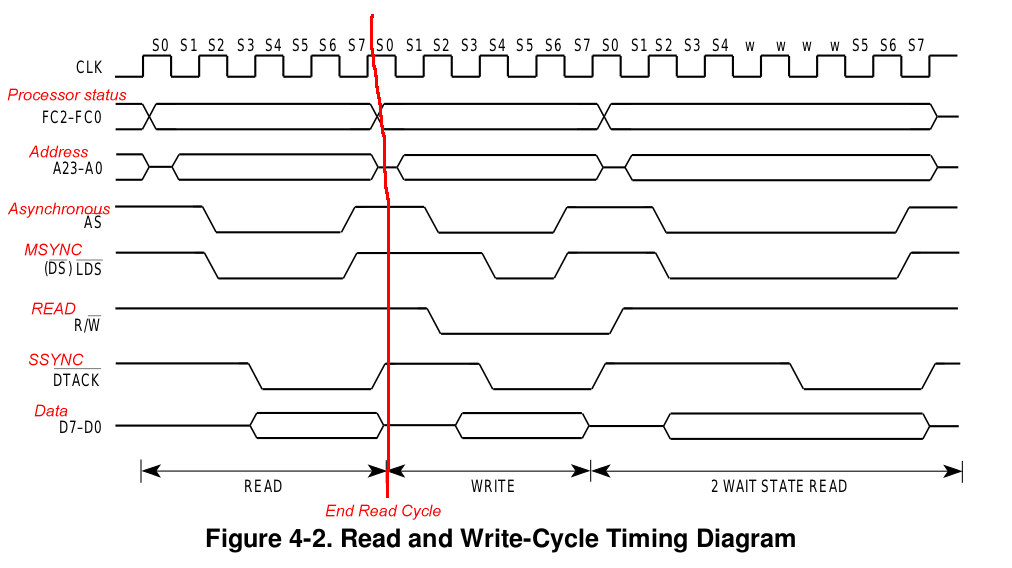

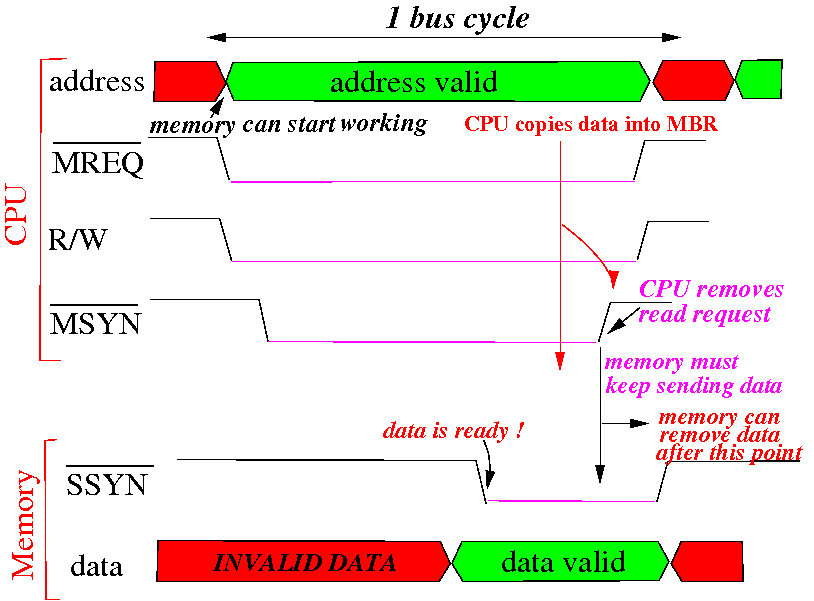

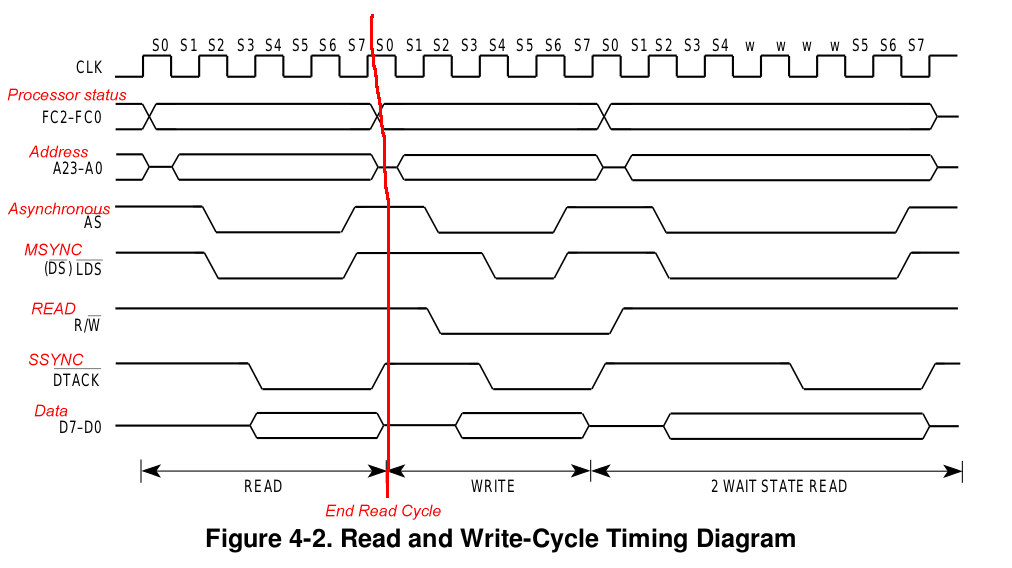

Actual example of a timing diagram (there are 3 operations in this diagram)

We will now study the timing diagram of the asynchronous READ protocol:

I will explain the timing diagram in a piece meal manner next....

The signals activated by the CPU and memory when executing the async READ procotol are:

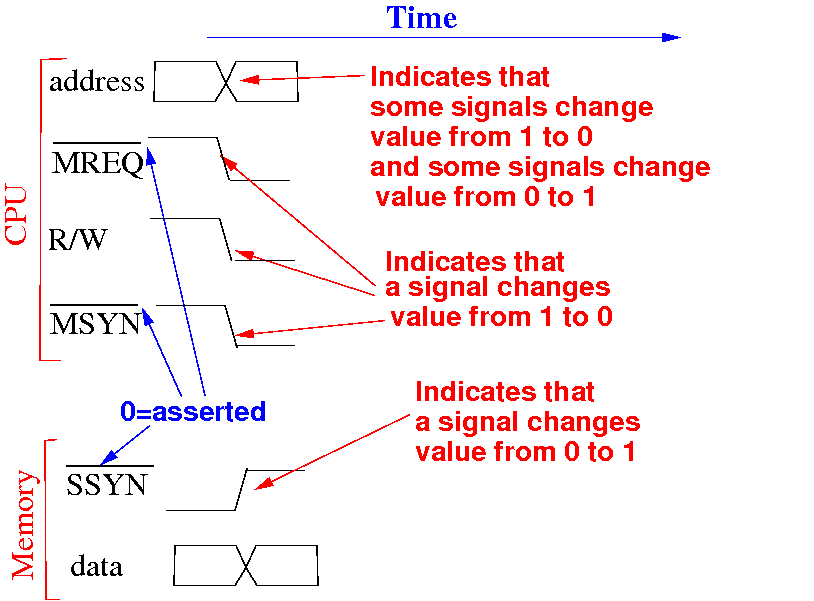

The meaning of the signal transitions in a timing diagram:

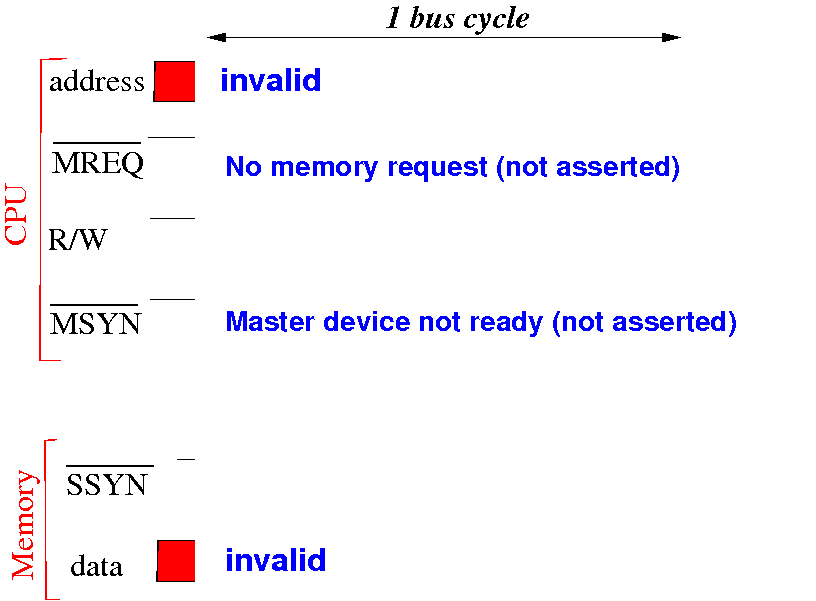

The signals at The start of an asynchronous READ protocol are as follows:

The CPU now starts a READ operation and runs the async READ protocol...

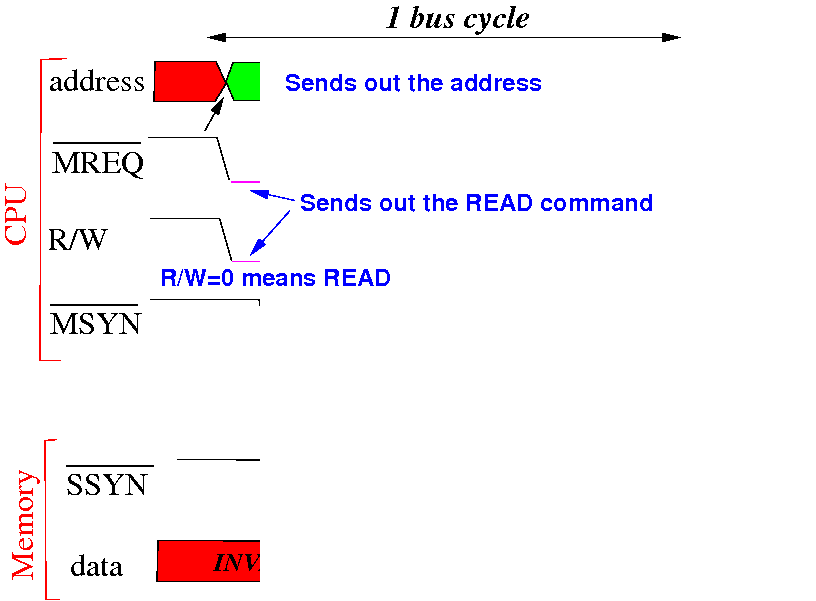

(1) the CPU sends out the address and a READ command:

The memory may start working on the request; but it will usually wait till the next step...

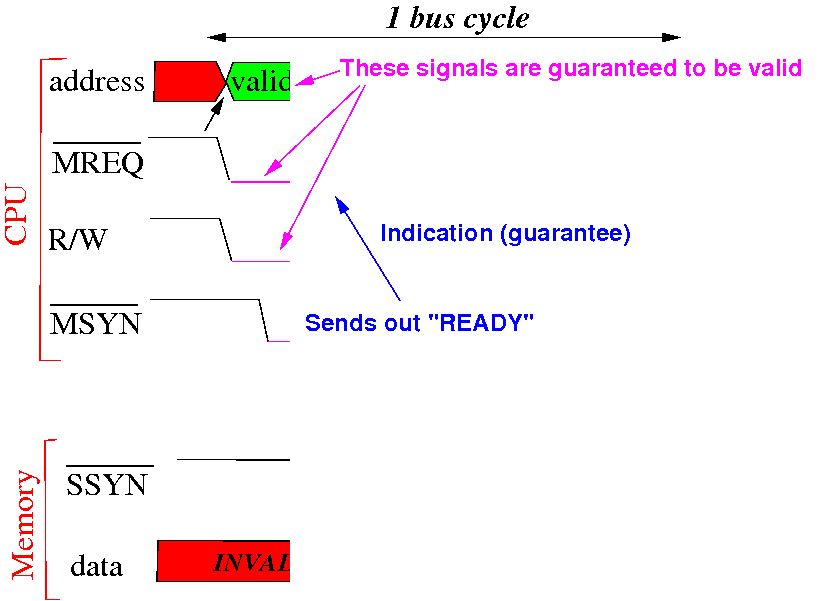

(2) the CPU asserts the MSYNC sigan to tell the memory that all signals are now valid:

The memory will now fetch the data requested in the READ operation...

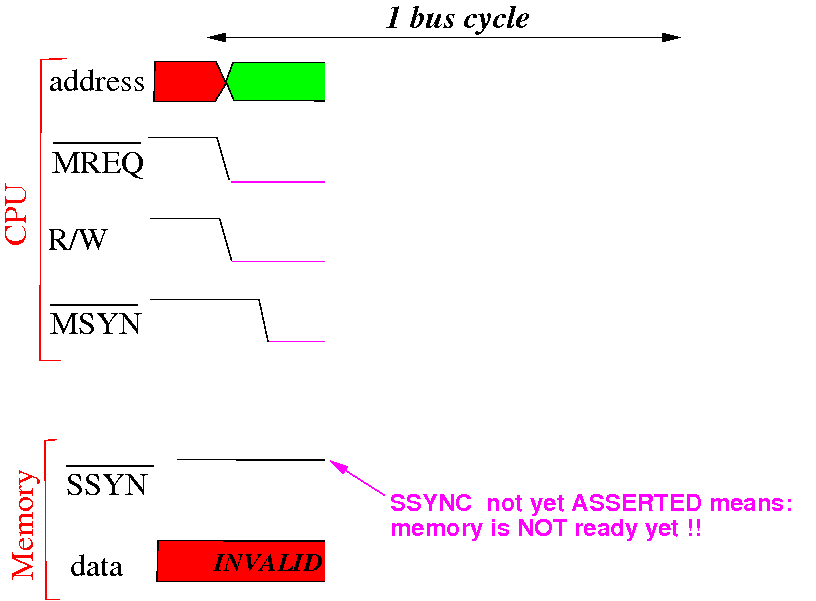

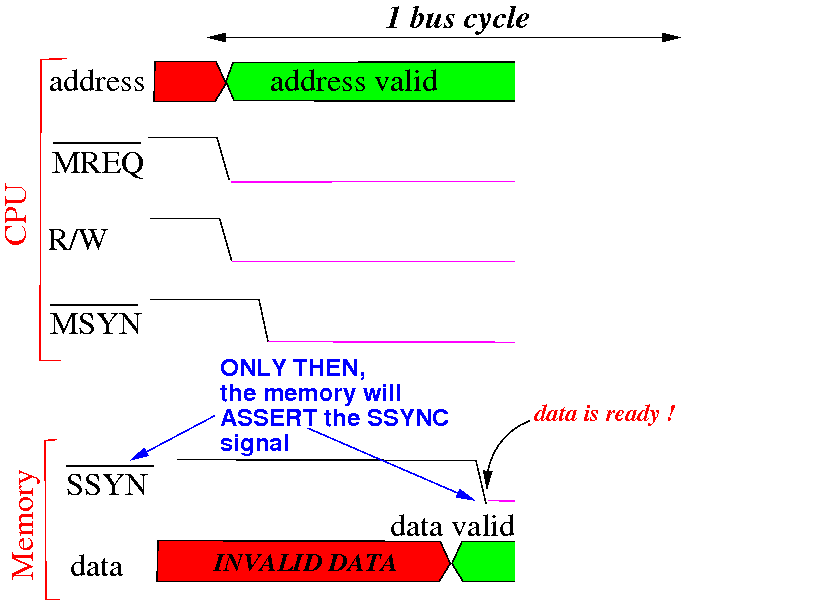

(3) the memory will now process the READ request:

The SSYNC signal will prevent the CPU from reading invalid data on the data bus !!!

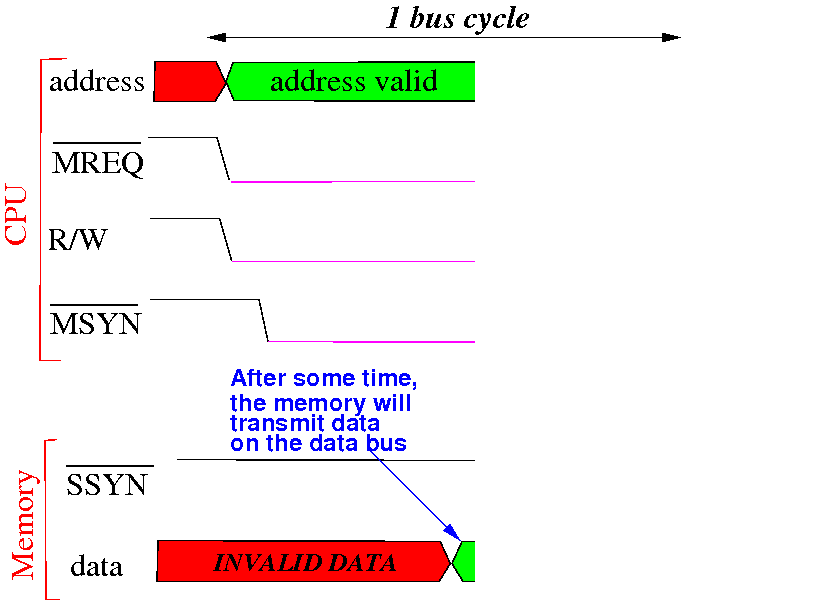

(4) after some processing delay, the memory will send the fetched data on the data bus:

At this moment, the CPU can not tell if the data is valid !!!

(5) the memory will certify the data correctness by asserting the SSYNC signal:

The SSYNC signal will trigger the CPU to continue with the next step !!!

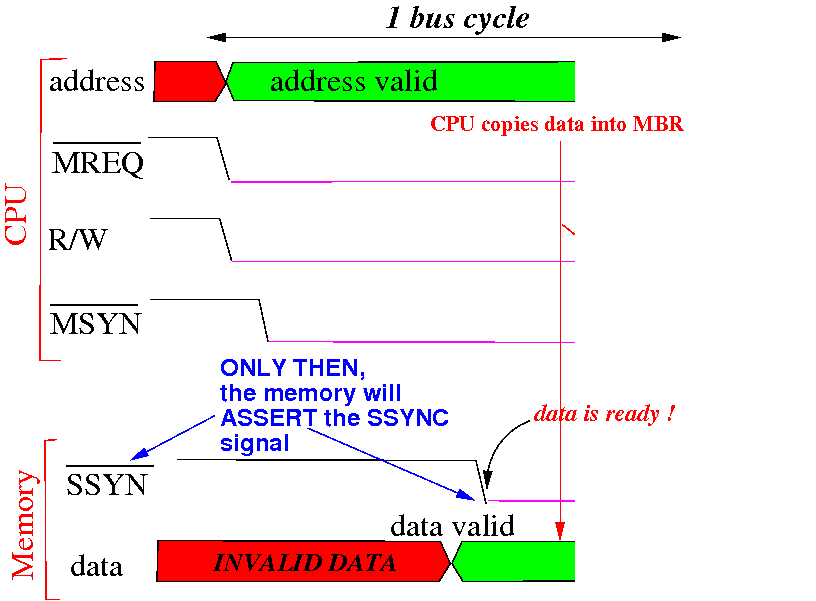

(6) the CPU will copy the data on the data bus into its MBR reg at the earliest possible time:

Note that the protocol can guarantee that the data on the data bus is correct !!

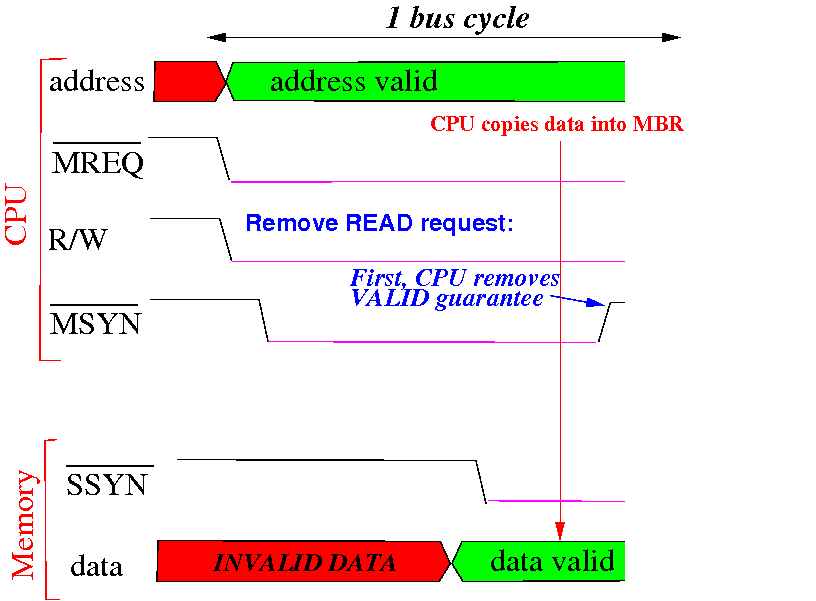

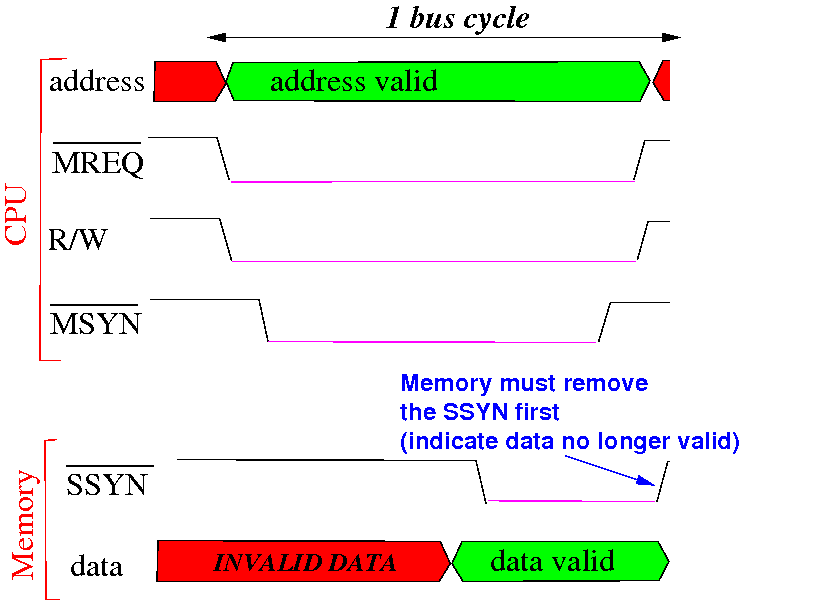

(7) the CPU must remove (withdraw) the READ request from the bus in a safe manner:

Unassert MSYNC first (MREQ and R/W cannot change while MSYNC is asserted)

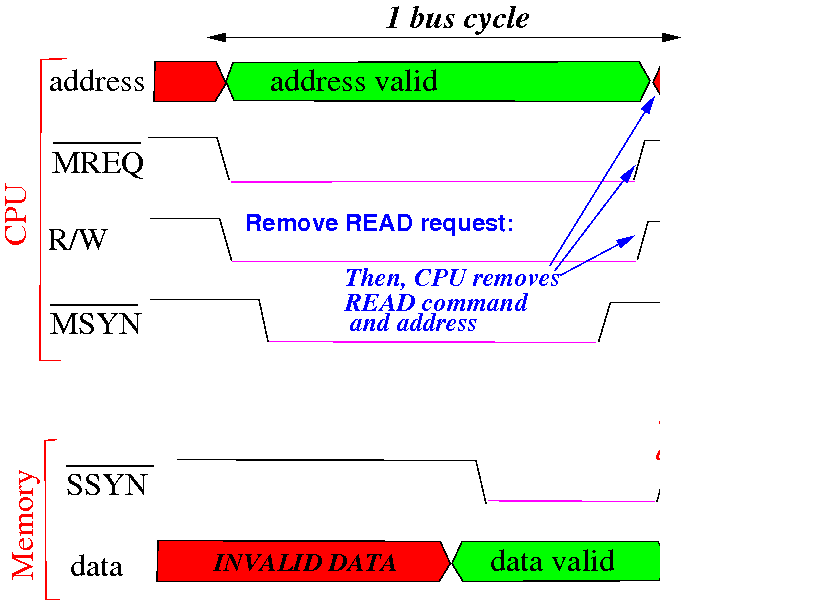

(7) the CPU must remove (withdraw) the READ request from the bus in a safe manner:

When MSYNC ("guaranteed correct") is unasserted, CPU can safely change the other signals

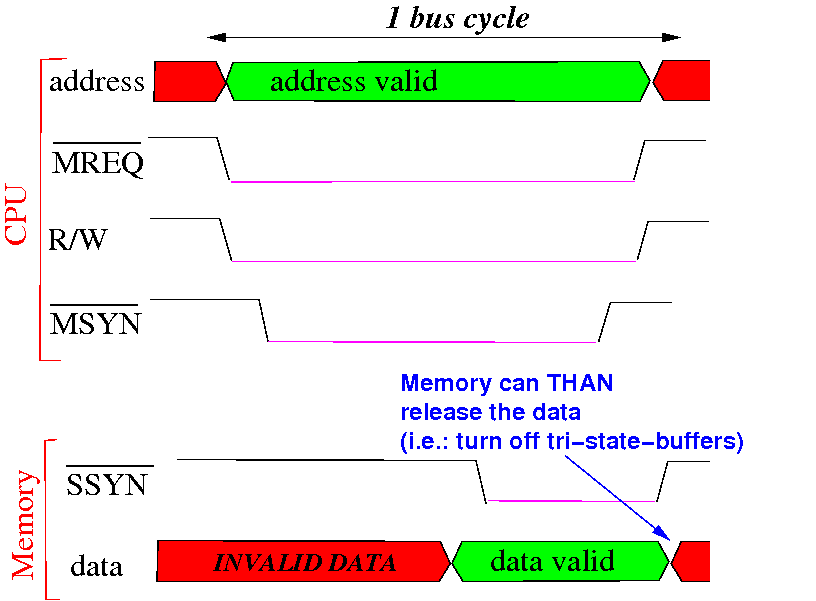

(8) the memory must remove (withdraw) the DATA response from the bus in a safe manner:

Unassert SSYNC first (the data cannot change while SSYNC is asserted)

(8) the memory must remove (withdraw) the DATA response from the bus in a safe manner:

When SSYNC ("data guaranteed correct") is unasserted, memory can safely remove the data

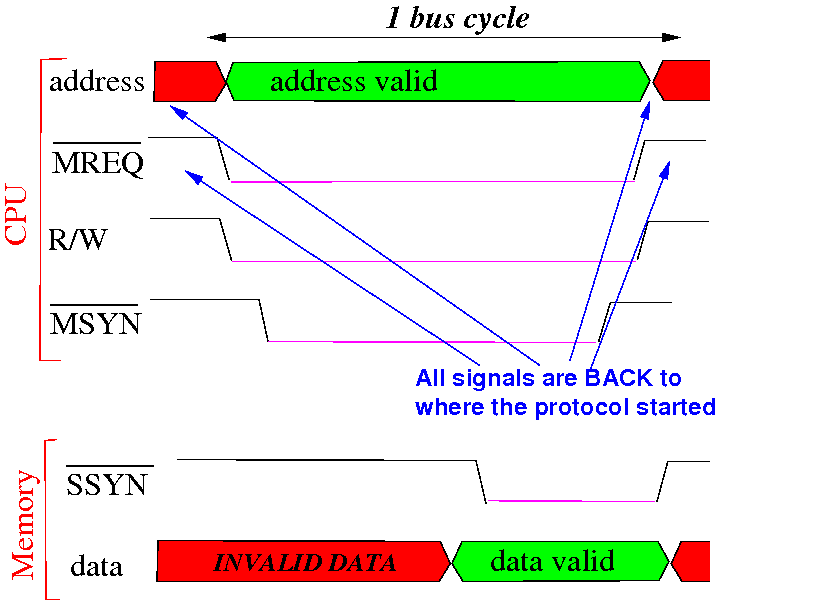

Notice that: all signals have returned to their original state !!

Therefore: a new bus cycle can start immediately !!!

Can you now read the READ procotol in the timing diagram of the M68000 processor:

The READ procotol is on the left of the diagram.

(The right side of the diagram contains a asynchronous READ procotol, one on a slower memory)

Initially, there are no signals asserted on the bus:

(1) the CPU sends out address and MREQ and R/W=0:

(2) the CPU asserts the MSYNC to indicate that the request signals are now valid:

(3) in response (to MSYNC), the memory fetches the requested data and send it on the databus:

(4) the memory then asserts SSYNC to tell the CPU that it's OK to read the data now:

Notice that the protocol guarantees that the CPU receives valid data on data bus:

(5) the CPU read the data and then: first de-assert MSYNC:

(5) the CPU then de-assert the other request signals:

(6) in response (to MSYNC), will de-assert the SSYNC signal first:

This means: data on data bus is invalid (even though it's still valid, that's OK)

(6) and the memory withdraws the data from the databus (shut of tri-state-buffers):

And the computer system is back to the initial state !!!

|